General Purpose I/O Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 13-11

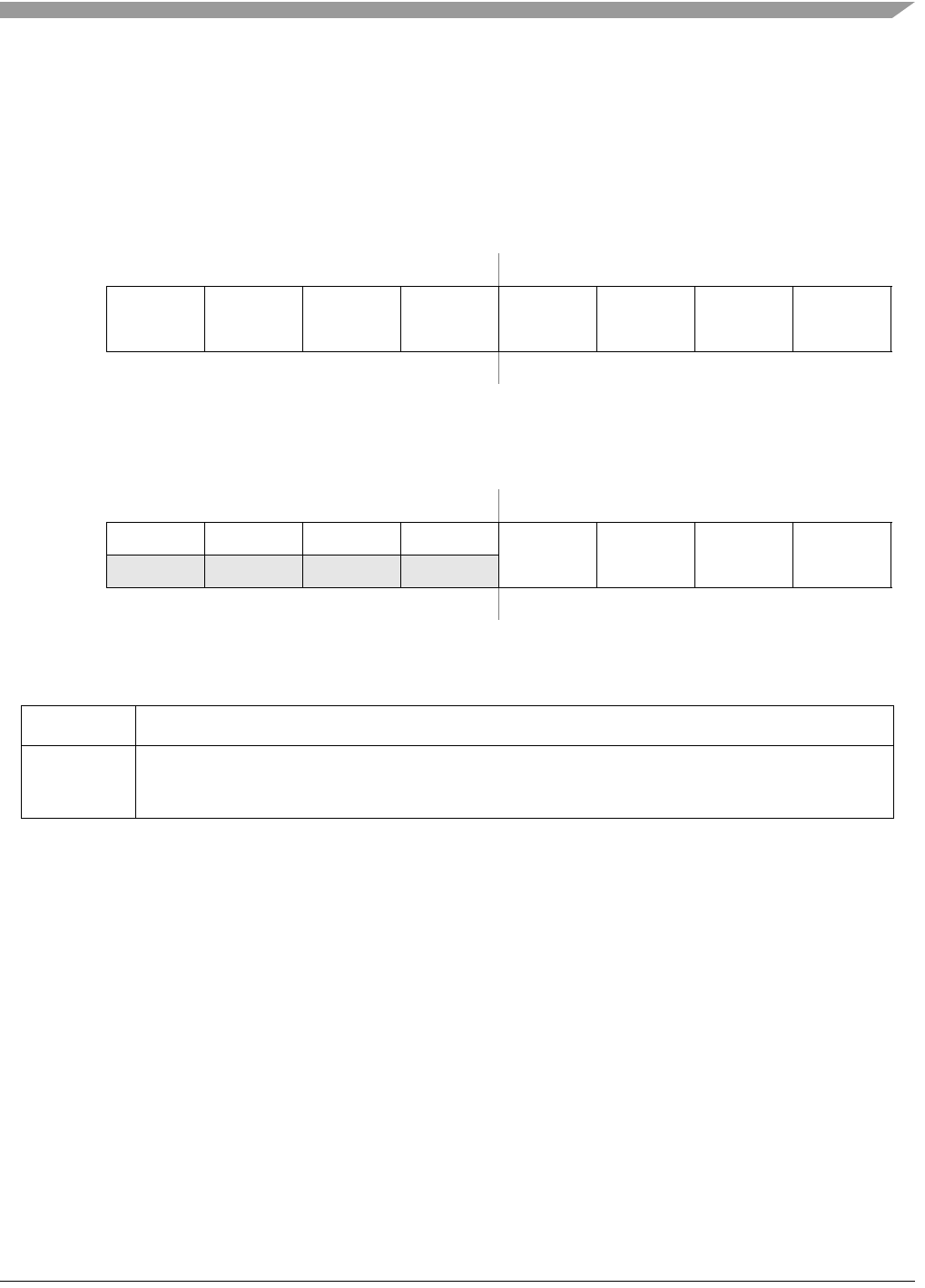

13.6.5.1 Dual-Function Pin Assignment Registers

The dual function pin assignment registers allow each pin controlled by each register bit to be configured

for the primary function or the GPIO function. The fields are described in Table 13-6, which applies to all

dual-function registers.

.

13.6.5.2 Quad Function Pin Assignment Registers

The quad function pin assignment registers allow each pin controlled by each register bit to be configured

for the primary, alternate 1 (secondary), alternate 2 (tertiary), and GPIO (quaternary) functions. The fields

are described in Table 13-7, which applies to all quad-function registers.

IPSBAR

Offsets:

0x10_0074 (PDDPAR)

0x10_006A (PANPAR)

Access: User read/write

76543210

R

PnPAR7 PnPAR6 PnPAR5 PnPAR4 PnPAR3 PnPAR2 PnPAR1 PnPAR0

W

Reset:00000000

Figure 13-22. Dual-Function Pin Assignment Registers with Bits 7:0 Implemented (PDDPAR, PANPAR)

IPSBAR

Offsets:

0x10_0070 (PTDPAR)

0x10_0073 (PUCPAR)

Access: User read/write

76543210

R 0 0 0 0

PnPAR3 PnPAR2 PnPAR1 PnPAR0

W

Reset:00000000

Figure 13-23. Dual-Function Pin Assignment Registers with Bits 3:0 Implemented (PTDPAR, PUCPAR)

Table 13-6. Dual-Function PnPAR Field Descriptions

Field Description

PnPAR x P nPARx pin assignment register bits.

1 Pin assumes the primary function

0 Pin assumes the GPIO function