Programmable Interrupt Timers (PIT0–PIT1)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 20-3

20.2.1 PIT Control and Status Register (PCSRn)

The PCSRn registers configure the corresponding timer’s operation.

2

User mode accesses to supervisor only addresses have no effect and result in a cycle termination transfer error.

IPSBAR

Offset:

0x15_0000 (PCSR0)

0x16_0000 (PCSR1)

Access: Supervisor

read/write

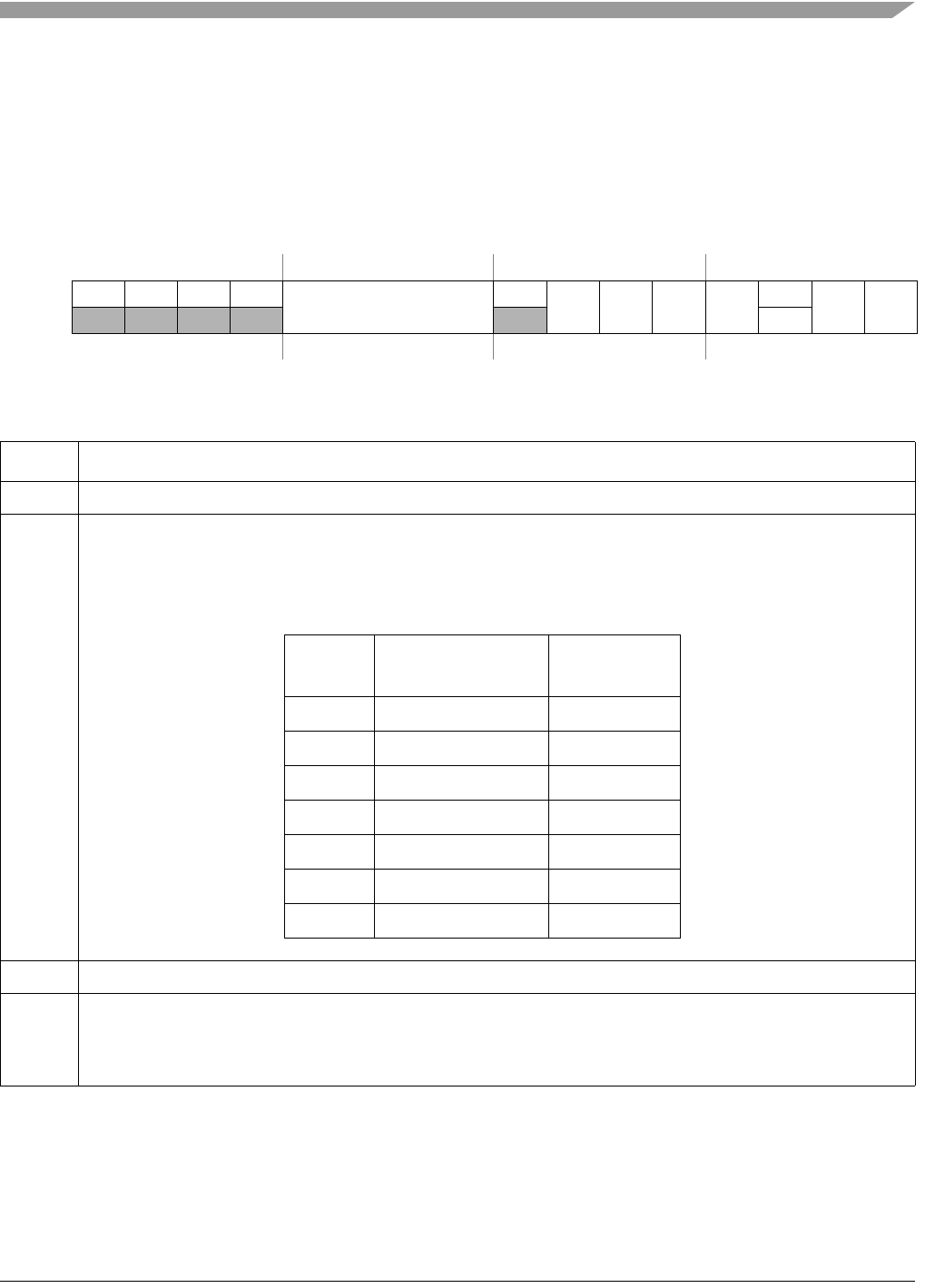

1514131211109876543210

R0000

PRE

0

DOZE DBG OVW PIE

PIF

RLD EN

W

w1c

Reset0000000000000000

Figure 20-2. PCSRn Register

Table 20-3. PCSRn Field Descriptions

Field Description

15–12 Reserved, must be cleared.

11–8

PRE

Prescaler. The read/write prescaler bits select the internal bus clock divisor to generate the PIT clock. To accurately

predict the timing of the next count, change the PRE[3:0] bits only when the enable bit (EN) is clear. Changing

PRE[3:0] resets the prescaler counter. System reset and the loading of a new value into the counter also reset the

prescaler counter. Setting the EN bit and writing to PRE[3:0] can be done in this same write cycle. Clearing the EN

bit stops the prescaler counter.

7 Reserved, must be cleared.

6

DOZE

Doze Mode Bit. The read/write DOZE bit controls the function of the PIT in doze mode. Reset clears DOZE.

0 PIT function not affected in doze mode

1 PIT function stopped in doze mode. When doze mode is exited, timer operation continues from the state it was in

before entering doze mode.

PRE

Internal Bus Clock

Divisor

Decimal

Equivalent

0000 2

0

1

0001 2

1

2

0010 2

2

4

... ... ...

1101 2

13

8192

1110 2

14

16384

1111 2

15

32768