Universal Serial Bus, OTG Capable Controller

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 15-39

15.7.3 Power

The USB-FS core is a fully synchronous static design. The power used by the design is dependant on the

application usage of the core. Applications that transfer more data or cause a greater number of packets to

be sent consumes a greater amount of power.

Because the design is synchronous and static, reducing the transitions on the clock net may conserve

power. This may be done in the following ways.

The first is to reduce the clock frequency to the USB module. The clock frequency may not be reduced

below the minimum recommended operating frequency of the USB module without first disabling the

USB operation and disconnecting (via software disconnect) the USB module from the USB bus.

Alternately, the clock may be shut off to the core to conserve power. Again, this may only be done after

the USB operations on the bus have been disabled and the device has been disconnected from the USB.

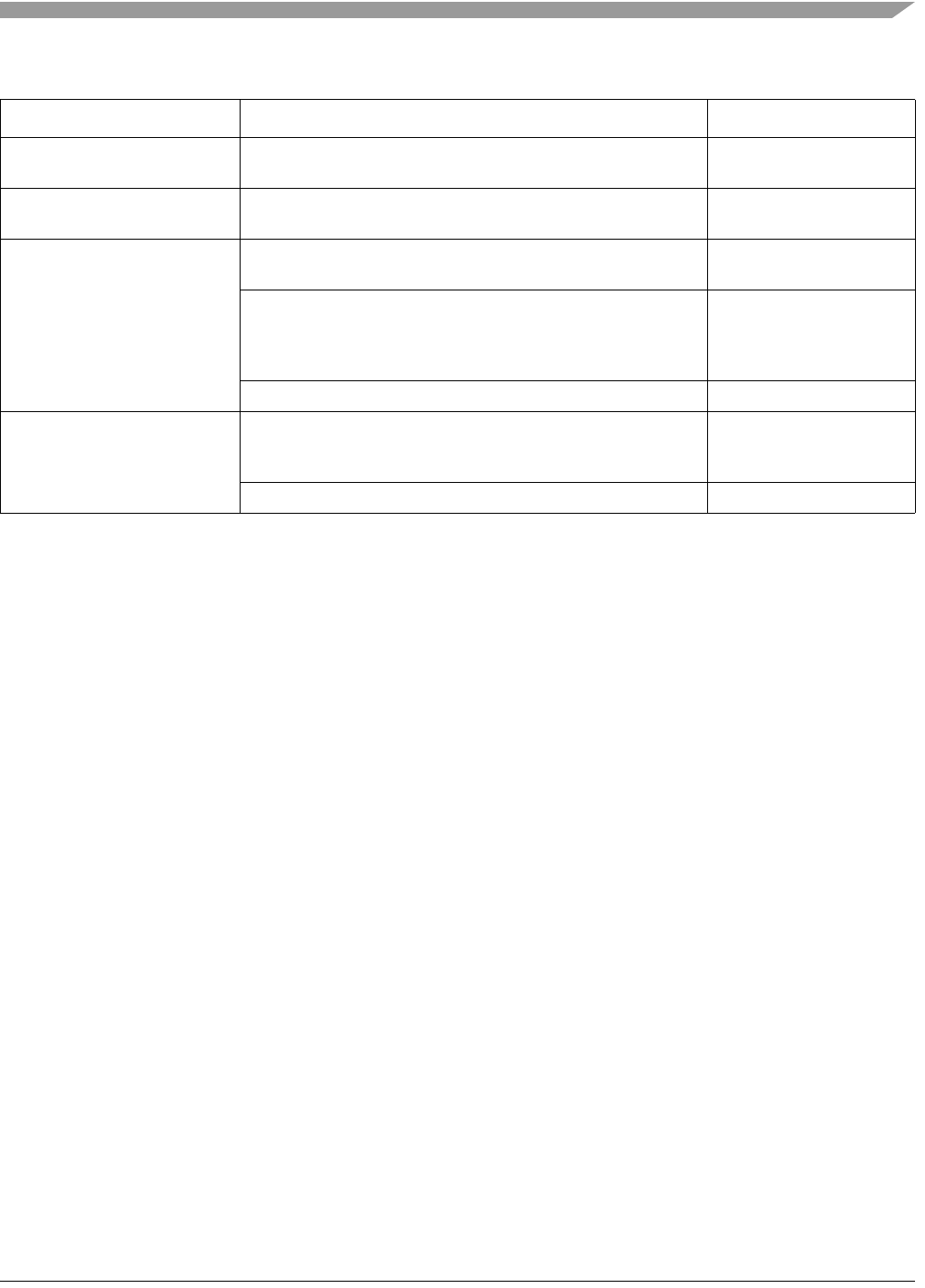

B_SRP_INIT If ID\ Interrupt or SRP Done (SRP must be done in less than 100

msecs.)

Go to B_IDLE

B_PERIPHERAL If HNP enabled and the bus is suspended and B wants the bus,

the B device can become the host.

Go to B_WAIT_ACON

Turn off DP_HIGH

B_WAIT_ACON If A connects, that is, an attach interrupt is received Go to B_HOST

Turn on Host Mode

If ID\ Interrupt or B_SESS_VLD/ Interrupt

If the cable changes or if VBUS goes away, the host doesn’t

support us.

Go to B_IDLE

Go to B_IDLE

If 3.125 ms expires or if a Resume occurs Go to B_PERIPHERAL

B_HOST If ID\ Interrupt or B_SESS_VLD\ Interrupt

If the cable changes or if VBUS goes away, the host doesn’t

support us.

Go to B_IDLE

If B application is done or A disconnects Go to B_PERIPHERAL

Table 15-39. State Descriptions for Figure 15-34 (continued)

State Action Response