DMA Timers (DTIM0–DTIM3)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

22-8 Freescale Semiconductor

22.3 Functional Description

22.3.1 Prescaler

The prescaler clock input is selected from the internal bus clock (f

sys

divided by 1 or 16) or from the

corresponding timer input, DTINn. DTINn is synchronized to the internal bus clock, and the

synchronization delay is between two and three internal bus clocks. The corresponding DTMRn[CLK]

selects the clock input source. A programmable prescaler divides the clock input by values from 1 to 256.

The prescaler output is an input to the 32-bit counter, DTCNn.

22.3.2 Capture Mode

Each DMA timer has a 32-bit timer capture register (DTCRn) that latches the counter value when the

corresponding input capture edge detector senses a defined DTINn transition. The capture edge bits

(DTMRn[CE]) select the type of transition that triggers the capture and sets the timer event register capture

event bit, DTERn[CAP]. If DTERn[CAP] and DTXMRn[DMAEN] are set, a DMA request is asserted. If

DTERn[CAP] is set and DTXMRn[DMAEN] is cleared, an interrupt is asserted.

22.3.3 Reference Compare

Each DMA timer can be configured to count up to a reference value, at which point DTERn[REF] is set.

If DTMRn[ORRI] is set and DTXMRn[DMAEN] is cleared, an interrupt is asserted. If DTMRn[ORRI]

and DTXMRn[DMAEN] are set, a DMA request is asserted. If the free run/restart bit DTMRn[FRR] is

set, a new count starts. If it is clear, the timer keeps running.

22.3.4 Output Mode

When a timer reaches the reference value selected by DTRR, it can send an output signal on DTOUTn.

DTOUTn can be an active-low pulse or a toggle of the current output, as selected by the DTMRn[OM] bit.

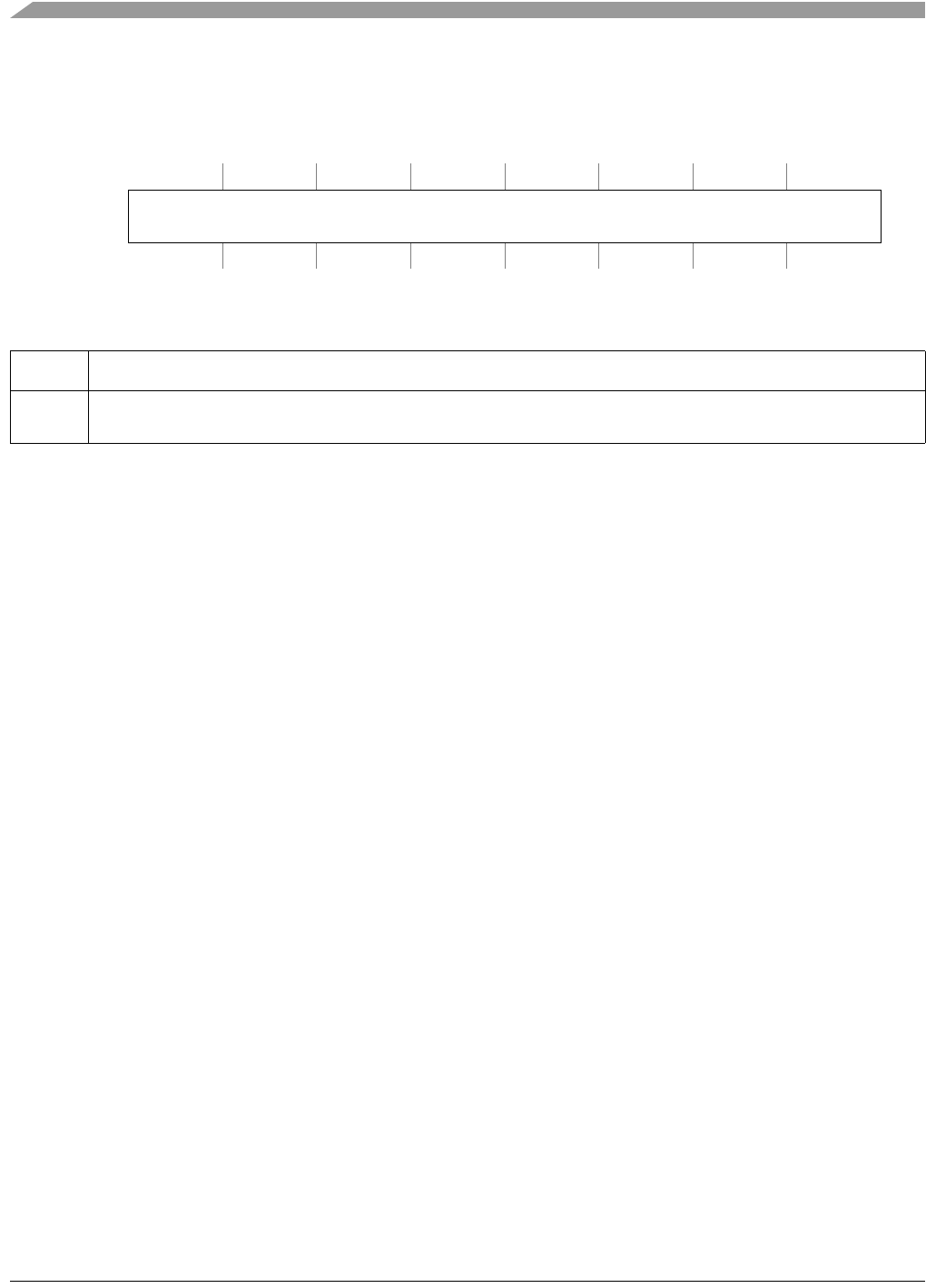

IPSBAR

Offset:

0x00_040C (DTCN0)

0x00_044C (DTCN1)

0x00_048C (DTCN2)

0x00_04CC (DTCN3)

Access: User read/write

313029282726252423222120191817161514131211109876543210

R

CNT (32-bit timer counter value count)

W

Reset00000000000000000000000000000000

Figure 22-7. DMA Timer Counters (DTCNn)

Table 22-7. DTCNn Field Descriptions

Field Description

31–0

CNT

Timer counter. Can be read at anytime without affecting counting. Any write to this field clears it.