LSI Specification

MB86617A

Rev.1.0 Fujitsu VLSI

108

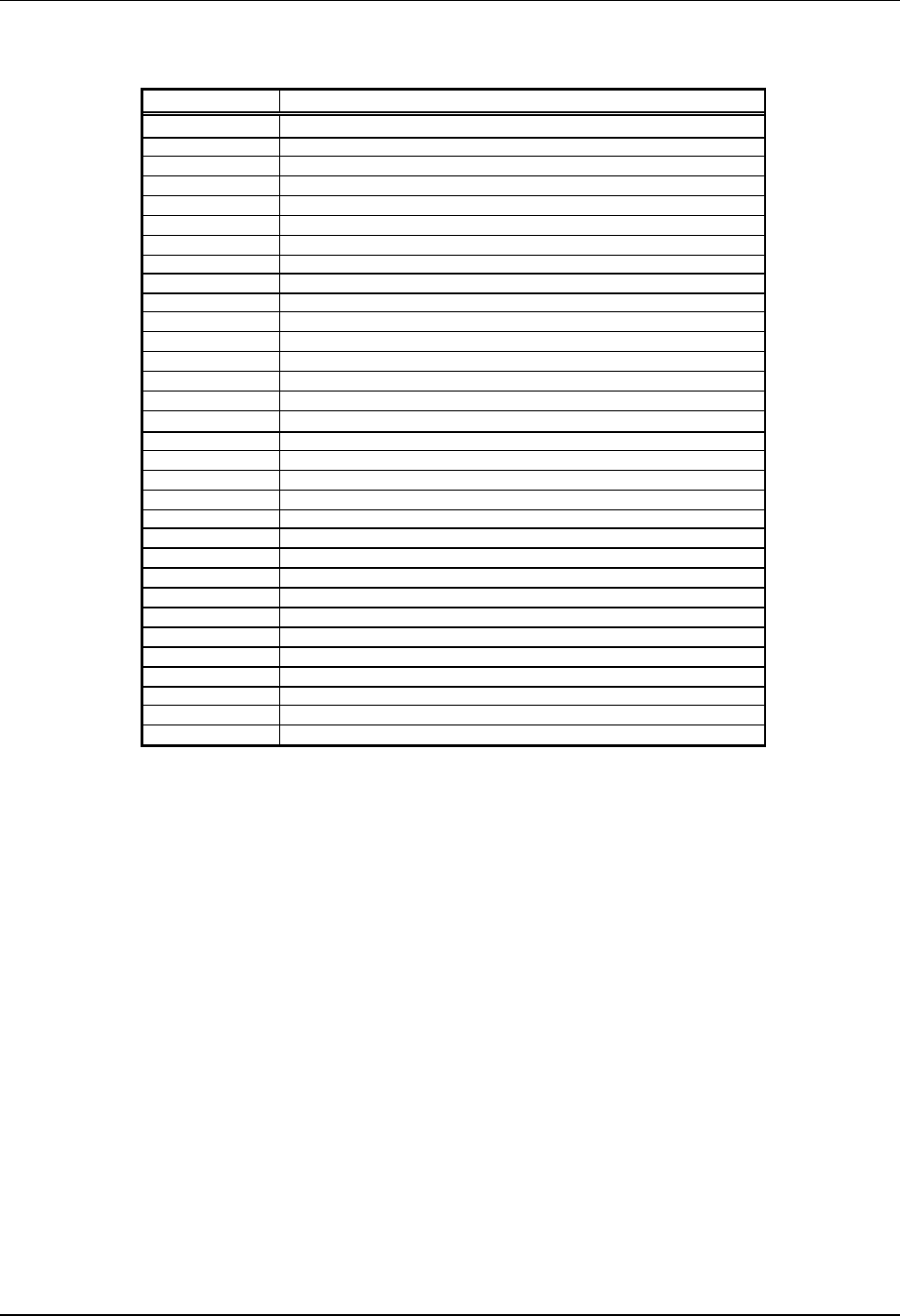

10.2. Interrupt

Interrupt Interrupt Item

INT1 Loop detected

INT2 Self-ID packet error

INT3 Bus reset complete

INT4 Bus reset detected

INT5 Isochronous packet receive error (A-ch)

INT6 Isochronous packet receive error (B-ch)

INT7 Isochronous cycle too long

INT8 Bus occupancy violation

INT9 Asynchronous packet received

INT10 CPIF output header is no 47h (Transmit)

INT11 Data length short error

INT12 Data length long error

INT13 Packet format error

INT14 Header CRC error

INT15 Data CRC error

INT16 Asynchronous receive FIFO full

INT17 Asynchronous packet send

INT18 Input CGMS or TSCH changed

INT19 Acknowledge missing

INT20 Acknowledge send

INT21 Receive EMI or ODD/EVEN changed

INT22 First packet received

INT23 Cycle start packet received

INT24 Cycle start packet send

INT25 Physical packet send

INT26 Extended PHY packet received

INT27 Physical configuration packet received

INT28 Link-on packet received

INT29 Self-ID packet received

INT30 Receive late occurred

INT31 Instruction abort

INT32 Transmit late occurred