LSI Specification

MB86617A

Rev.1.0 Fujitsu VLSI

87

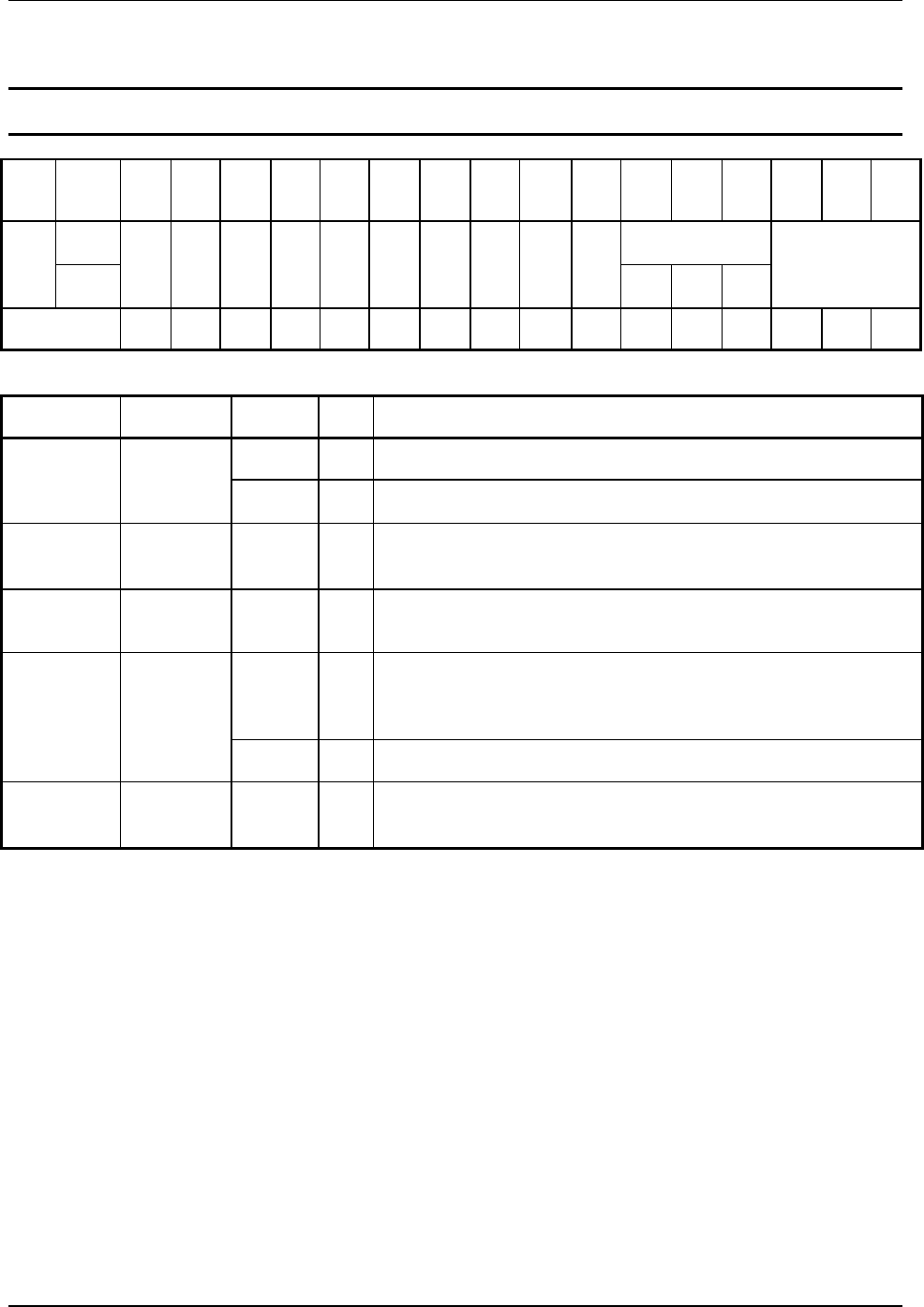

8.6. Physical register #04 (read/write)

Physical Register#04 is the register that sets the parameter of Self-ID packet to be transmitted by this node.

phy/

link-

addr

R/W

Bit

15

Bit

14

Bit

13

Bit

12

Bit

11

Bit

10

Bit

9

Bit

8

Bit

7

Bit

6

Bit

5

Bit

4

Bit

3

Bit

2

Bit

1

Bit

0

R Jitter

08 h

W

- - - - - - - -

Link_a

ctive

Conte

nder

- - -

Pwr _class

Initial Value ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘1’ ‘1’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’

<< Description of Each Bit

BIT Bit Name Action Value Function

Read - Always indicate ‘0’.

15 - 8 reserved

Write - Always write in ‘0’.

7

Link_active

Note 1)

Read/

Write

-

Set L bit (Link_active) value of Self-ID packet automatically transmitted by this

node with the system power ON.

6

Contender

Note 2)

Read/

Write

-

Set c bit (CONTENDER) value of Self-ID packet automatically transmitted by this

node with the system power ON.

Read -

Indicate Jitter value at receive signal repeat.

(MSB : 5 , LSB : 3)

Always indicates fixed value “000 b”. 5 - 3 Jitter

Write - Always write in ‘0’.

2 - 0

Pwr _class

Note 3)

Read/

Write

-

Set pwr field (POWER_CLASS) value of Self-ID packet automatically transmitted

by this node with the system power ON.

Note 1) L bit value of Self-ID packet that is automatically transmitted by this node with the cable supply power ON is always set at ‘0’

regardless of the setting of this bit.

Note 2) c bit value of Self-ID packet that is automatically transmitted by this node with the cable supply power ON is always set at ‘0’

regardless of the setting of this bit.

Note 3) pwr field value of Self-ID packet which is automatically transmitted by this node with the cable supply power ON is always set

at the value of PWR3 - 1 terminal regardless of the setting of this bit.