LSI Specification

MB86617A

Rev.1.0 Fujitsu VLSI

123

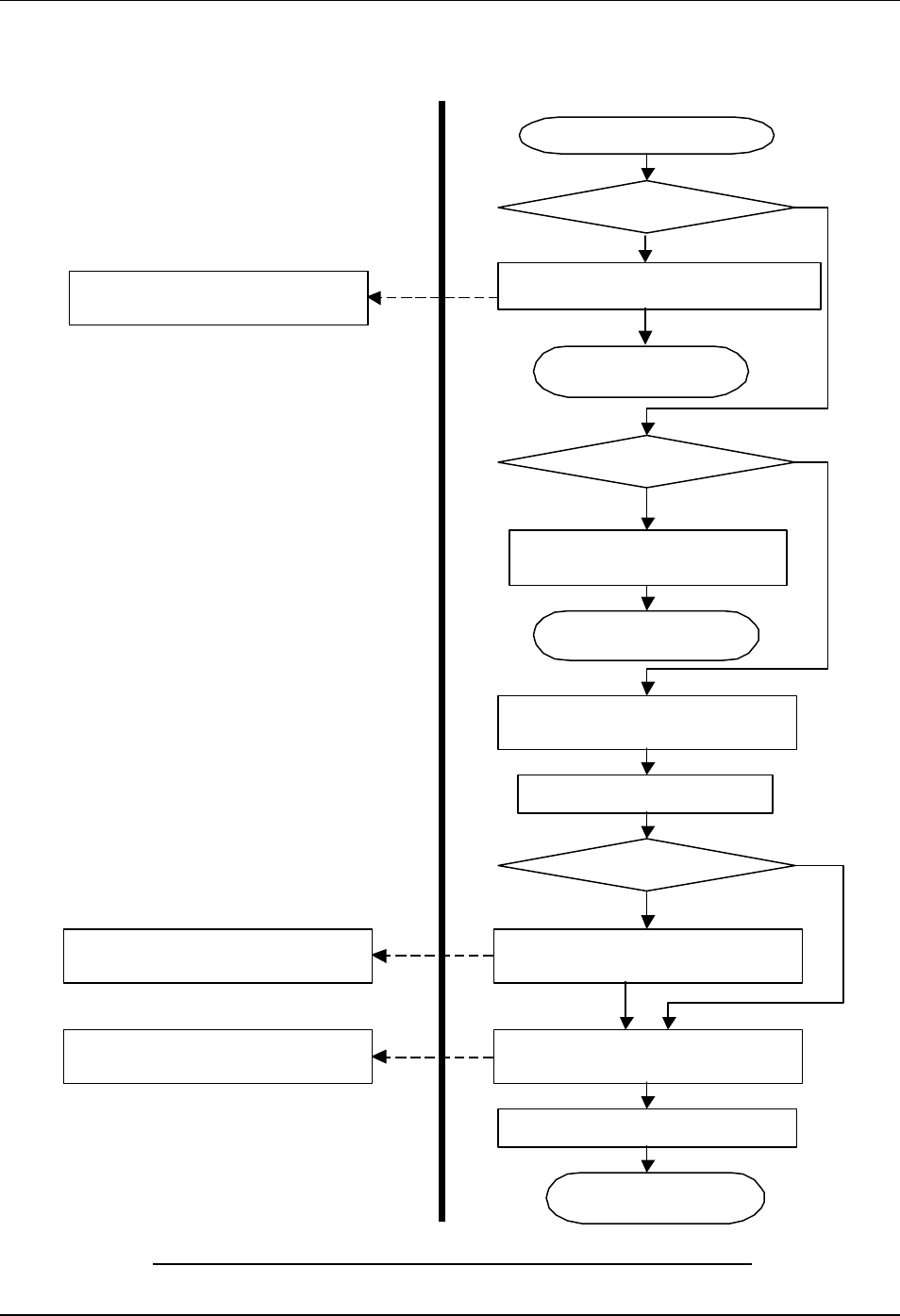

<< Flow chart for received data before storing in Asynchronous receive FIFO

<Host> <Device>

Figure 11.4.1 Flow example for received data before storing in Asynchronous receive FIFO

Receive packet to self-node.

Report Header CRC Error(INT14)

interrupt and duscard received packet.

Store Asynchronous packet into

Async hronous receive buffer.

Check Header CRC.

Transmit Acknowledge packet

Report Asynchronous packet receive

(INT9) interrupt(assert XINT).

NG

‘1’

recv busy bit

Transmit “Ack_busy_X” and

discard received packet.

recv busy bit=1

Report Asynchronous Receive FIFO full

(INT16) interrupt(assert XINT).

Read Asynchronous Receive FIFO

full(INT16)

interrupt.

Read Asynchronous packet

received(INT9)

interrupt.

OK

Read Header CRC Error (INT14)

interrupt.

Receive buffer=full

‘0’

Packet receiving process

completed

Packet receiving process

completed

Packet receiving process

completed

Yes

No