LSI Specification

MB86617A

Rev.1.0 Fujitsu VLSI

19

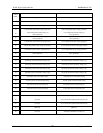

Chapter 6 Internal Register

This chapter explains the MB86617A internal register.

Note that the access of internal register is applied only 16 bits access.

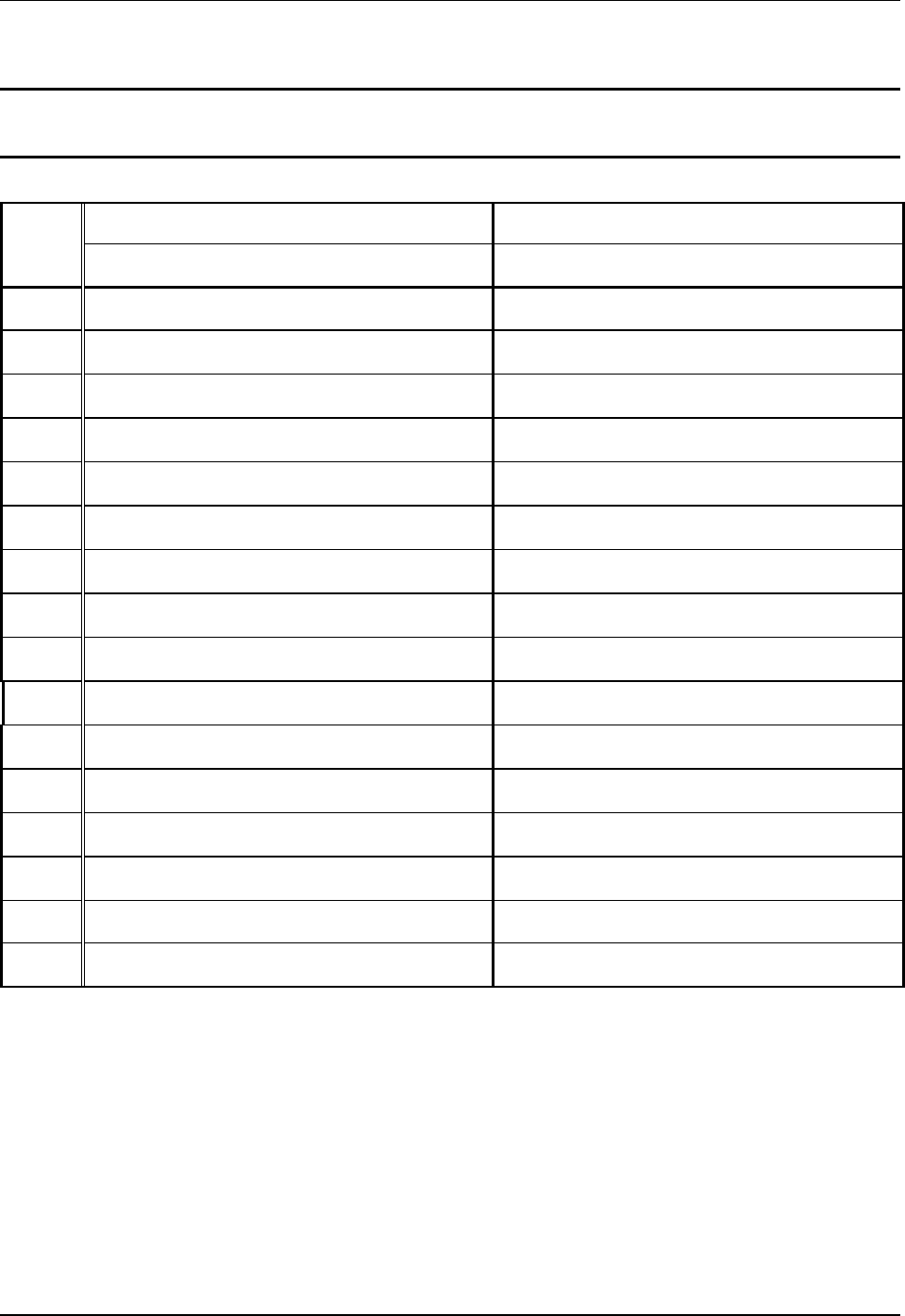

WRITE READ

Address

(HEX)

Register Name Register Name

00 mode-control mode-control

02 (reserved) flag & status

04 Instruction-fetch Instruction-fetch

06 Interrupt-mask setting [A] Interrupt indicate [A]

08 Interrupt-mask setting [B] Interrupt indicate [B]

0A (reserved) Receive Acknowledge

0C A-buffer data port transmit A-buffer data port receive

0E (reserved) (reserved)

10 TSP transmit information setting [A] TSP transmit information setting [A]

12 TSP transmit information setting [B] TSP transmit information setting [B]

14 transmit offset setting [A] (upper) transmit offset setting [A] (upper)

16 transmit offset setting [A] (lower) transmit offset setting [A] (lower)

18 transmit offset setting [B] (upper) transmit offset setting [B] (upper)

1A transmit offset setting [B] (lower) transmit offset setting [B] (lower)

1C TSP receive information setting TSP receive information setting

1E

transmit DSS packet header setting [A]

(most significant)

receive DSS packet header setting [A]

(most significant)