LSI Specification

MB86617A

Rev.1.0 Fujitsu VLSI

62

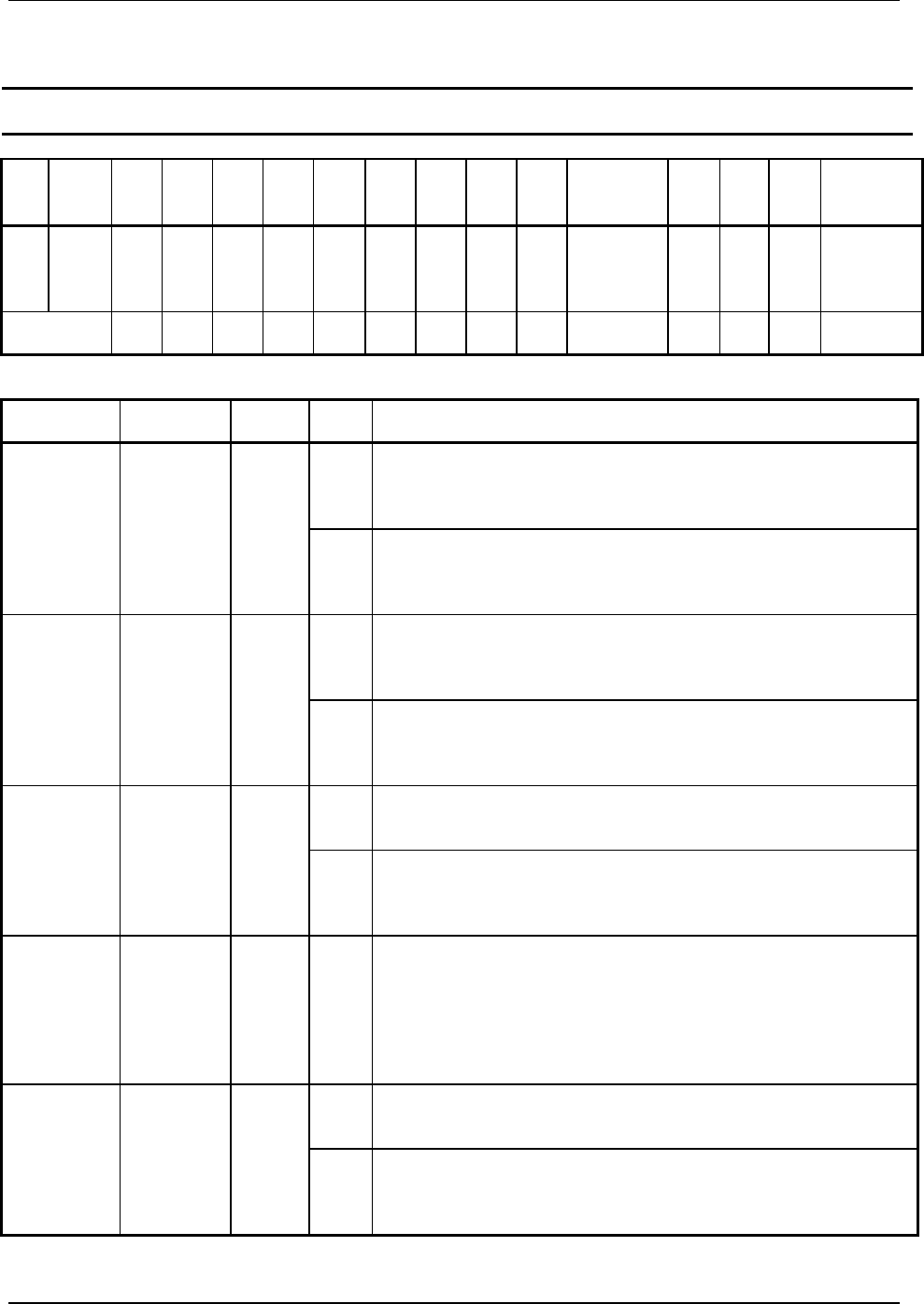

7.28. Data Bridge Transmit/Receive Status Register [A]

Data bridge transmit/receive status register indicates status of packet to be transmitted/received by bridge-Ach.

AD R/W

Bit

15

Bit

14

Bit

13

Bit

12

Bit

11

Bit

10

Bit

9

Bit

8

Bit

7

Bit

6

Bit

5

Bit

4

Bit

3

Bit

2

Bit

1

Bit

0

4Eh R

Tx

busy -

A

Rx

busy -

A

Rx

1STP-

A

Rx

EMI

chg-A

Rx o/e

chg-A

Rx

dlen

err-A

-

Tx

late-A

Rx

late-A

Rx 56

err-A

Rx

stype

err-A

BRG

FIFO

full -A

BRG

FIFO

emp-

A

Rx

DBC

err-A

Rx

CIP

err-A

Rx

FMT

err-A

Initial Value ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘1’ ‘0’ ‘0’ ‘0’

BIT Bit Name Action Value Function

0

Indicates that bridge-Ach is not in the process of transmit.

Indicates ‘0’ when Tx end-A (10h-bit14) is set at ‘1’ and transmit process is

stopped.

15 Tx busy-A Read

1

Indicates that bridge-Ach is in the process of transmit.

Indicates ‘1’ when Tx start -A (10h-bit15) is set at ‘1’ and transmit process is

started.

0

Indicates that bridge-Ach is not in the process of receive.

Indicates ‘0’ when Rx end-A (3Ch -bit6) is set at ‘1’ and receive process is stopped.

14 Rx busy-A Read

1

Indicates that bridge-Ach is in the process of receive.

Indicates ‘1’ when Rx start-A (3Ch -bit7) is set at ‘1’ and receive process is started.

0

Indicates that Isochronous packet received after starting receive process is not the

first packet received.

13 Rx 1STP-A Read

1

Indicates that the first Isochronous packet is received after receive process is

started.

Clears to ‘0’ by lead of this register.

0

Indicates that EMI information of received Isochronous packet header is not

changed.

12

Rx EMI

chg-A

Read

1

Indicates that EMI informatio n of received Isochronous packet header has changed

from just former EMI information of packet received by Isochronous-cycle.

Clears to ‘0’ by lead of this register.

0

Indicates that odd/even information of received Isochronous packet header is not

changed.

11 Rx o/e chg-A Read

1

Indicates that odd/even information of received Isochronous packet header has

changed from just former odd/even information of packet received by

Isochronous-cycle.

Clears to ‘0’ by lead of this register.