LSI Specification

MB86617A

Rev.1.0 Fujitsu VLSI

4

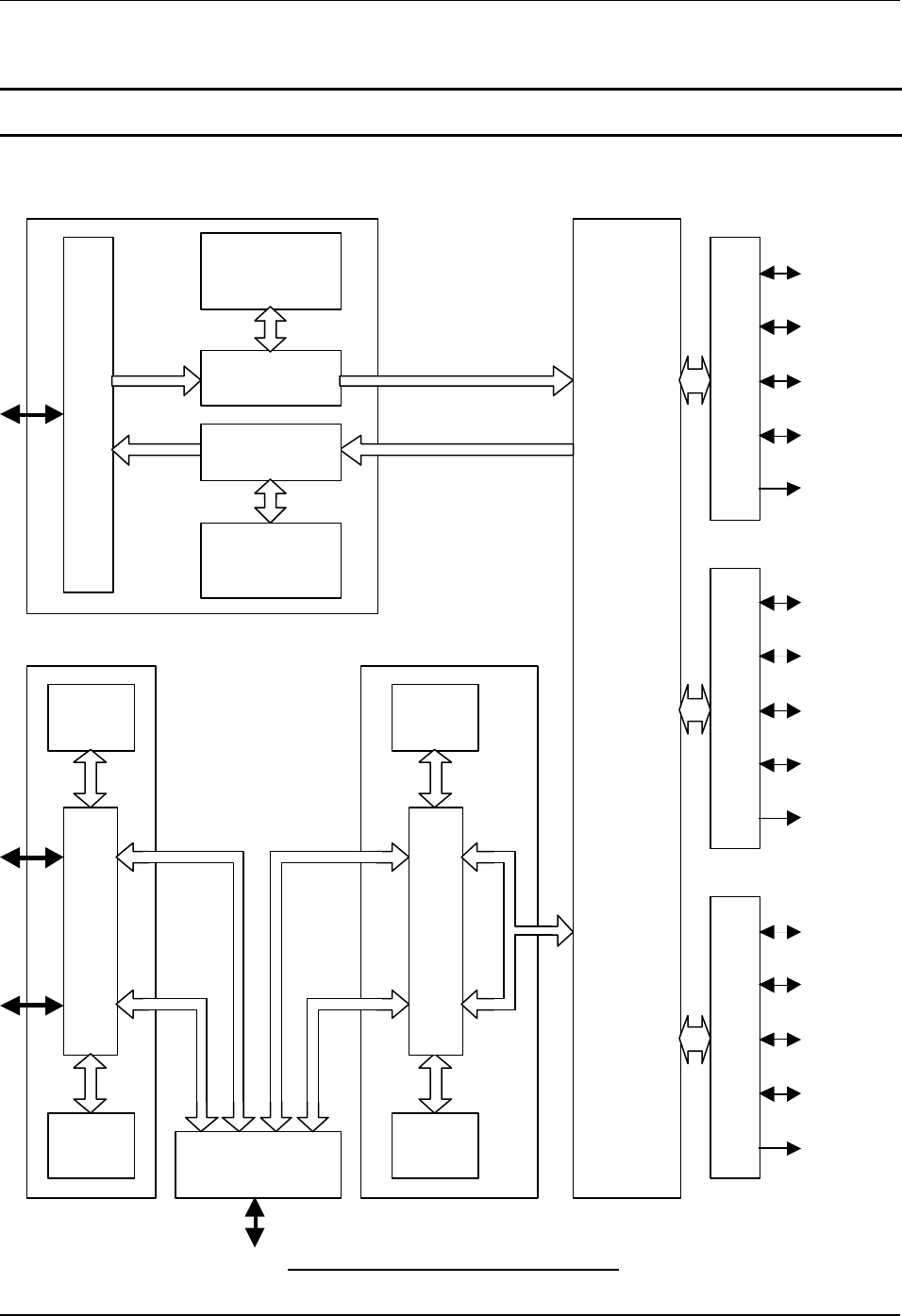

3.1. Block Diagram

MB86617A block diagram is shown below.

<< Normal Operation Mode

Fig.3.1.1 Block Diagram - Normal Operation Mode -

1394 Interface (Port 0)

TPA0

XTPA0

TPB0

XTPB0

TPBIAS0

1394 Interface (Port 1)

TPA1

XTPA1

TPB1

XTPB1

TPBIAS1

1394 Interface (Port 2)

TPA2

XTPA2

TPB2

XTPB2

TPBIAS2

PHY/

LINK

Layer

Control

Circuit

CP IC

Interface

FIFO

(2KByte)

FIFO

(2KByte)

Asynch Transmit

Exclusive FIFO

(256 byte)

Asynch Transmit

Exclusive FIFO

(256 byte)

TSP IC Interface

FIFO

(2KByte)

FIFO

(2KByte)

Asynch Transmit

Packet Process

Host Interface

Asynch Transmit

Packet Process

Data Bridge