LSI Specification

MB86617A

Rev.1.0 Fujitsu VLSI

127

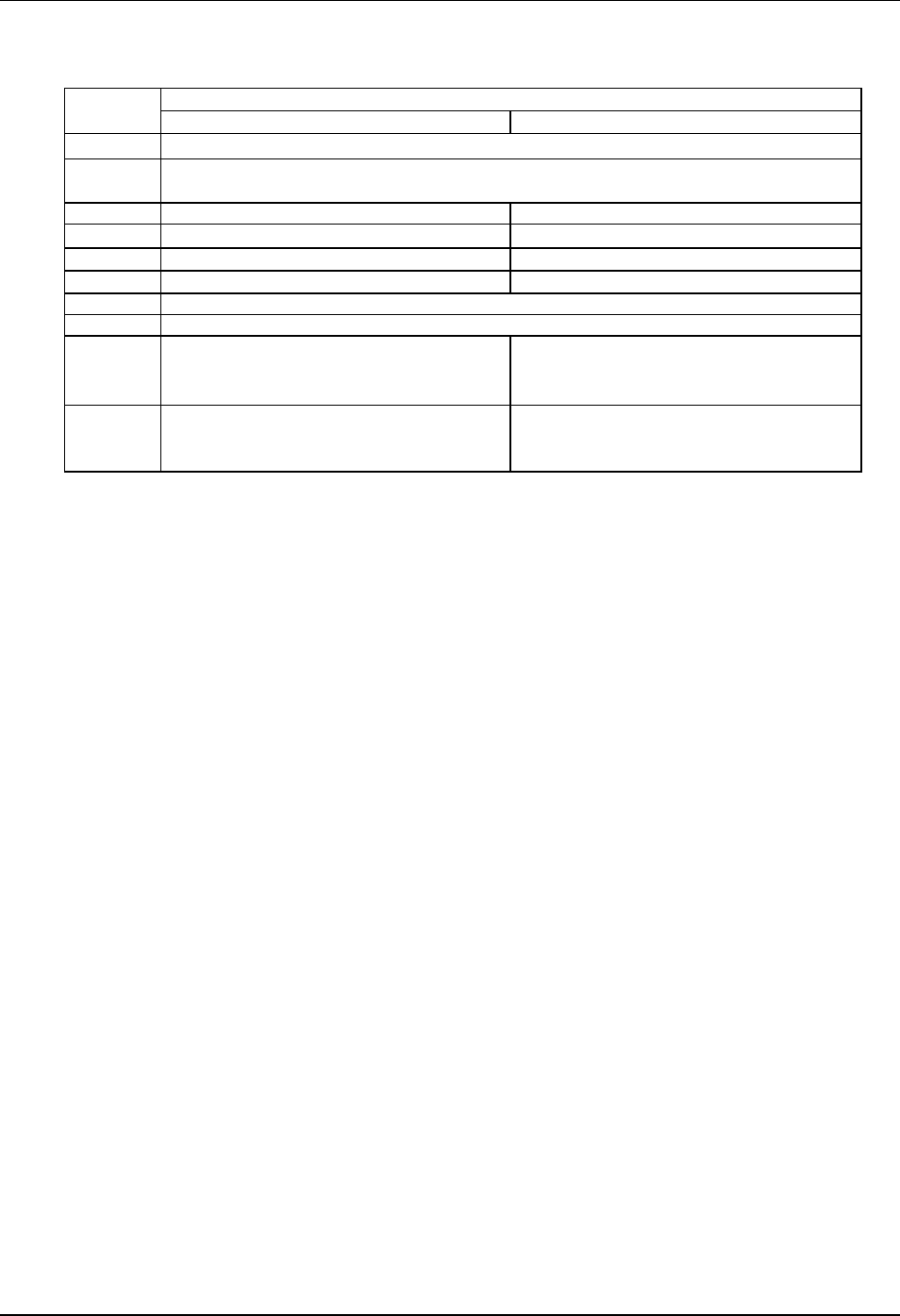

(Note)Register and bit necessary for transmitting are as follows.

Data

Address

MPEG-TS DSS

00h TSPSB=0, CPSB=0

14h,16h Set value of transmit Offset(Ach).

18h,1Ah Set value of transmit Offset (Bch)

34h DBSA=06h, FNA=3h DBSA=09h, FNA=2h

36h TXFMTA=20h, TXCHA(Iso channel No.) TXFMTA=21h, TXCHA(Iso channel No.)

38h DBSB=06h, FNB=3h DBSB=09h, FNB=2h

3Ah TXFMTB=20h, TXCHB(Iso channel No.) TXFMTB=21h, TXCHB(Iso channel No.)

40h Set criteria for Late packet (Ach).

42h Set criteria for Late packet (Bch).

10h

Set at Ach transmitting.

TXSTA=1, TFA

Set at Ach transmitting.

TXSTA=1, TFA, TXFMTA=1,

IDSIZEA=1(DSS130)

12h

Set at Bch transmitting.

TXSTB=1, TFB

Set at Bch transmitting.

TXSTB=1, TFB, TXFMTB=1,

IDSIZEB=1(DSS130)