7-41

CAN SERIAL COMMUNICATIONS CONTROLLER

7.9 DESIGN CONSIDERATIONS

This section outlines design considerations for the CAN controller.

7.9.1 Hardware Reset

A hardware reset clears the error management counters and the bus-off state and leaves the reg-

isters with the values listed in Table 7-14.

7.9.2 Software Initialization

The software initialization state allows software to configure the CAN controller’s RAM without

risk of messages being received or transmitted during this time. Setting the INIT bit in the control

register causes the CAN controller to enter the software initialization state. Either a hardware re-

set or a software write can set the INIT bit. While INIT is set, all message transfers to and from

the CAN controller are stopped and the error counters and bit timing registers are unchanged.

Your software should clear the INIT bit to cause the CAN controller to exit the software initial-

ization state. At this time, the CAN controller synchronizes itself to the CAN bus by waiting for

a bus idle state (11 consecutive recessive bits) before participating in bus activities.

7.9.3 Bus-off State

If an error counter reaches 256, the CAN controller isolates itself from the CAN bus, sets the

BUSOFF bit in the status register, and sets the INIT bit in the control register. While INIT is set,

all message transfers to and from the CAN controller are stopped; the error counters and bit tim-

ing registers are unchanged. Software must clear the INIT bit to initiate the bus-off recovery se-

quence.

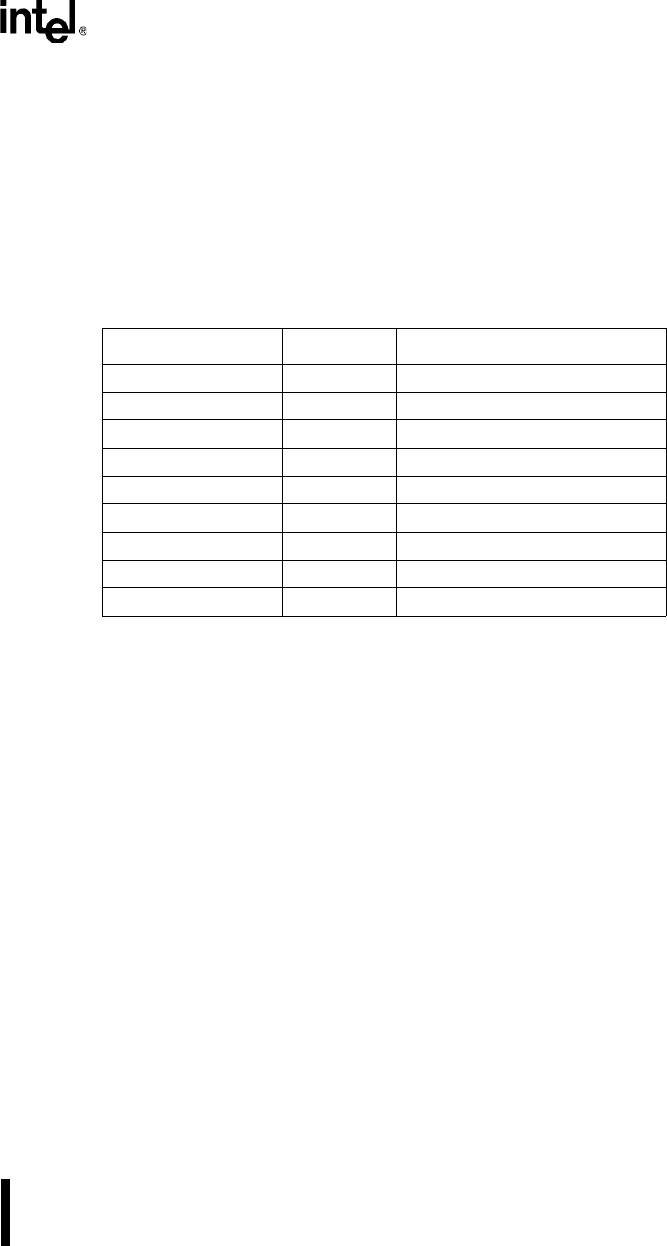

Table 7-14. Register Values Following Reset

Register Hex Address Reset Value

Control 1E00 01H

Status 1E01 undefined

Standard Global Mask 1E06–1E07 unchanged (undefined at power-up)

Extended Global Mask 1E08–1E0B unchanged (undefined at power-up)

Message 15 Mask 1E0C–1E0F unchanged (undefined at power-up)

Bit Timing 0 1E3F unchanged (undefined at power-up)

Bit Timing 1 1E4F unchanged (undefined at power-up)

Interrupt 1E5F 00H

Message Object

x

1E

x

0–1E

x

E unchanged (undefined at power-up)