87C196CB SUPPLEMENT

7-14

1 IE Interrupt Enable

This bit globally enables and disables interrupts (error, status-change, and

message object transmit and receive interrupts).

0 = disable interrupts

1 = enable interrupts

When the IE bit is set, an interrupt is generated only if the corresponding

interrupt source’s enable bit (EIE or SIE in CAN_CON; TXIE or RXIE in

CAN_MSG

x

_CON0) is also set. If the IE bit is clear, an interrupt request

updates the CAN interrupt pending register, but does not generate an

interrupt.

0 INIT Software Initialization Enable

Setting this bit isolates the CAN bus from the system. (If a transfer is in

progress, it completes, but no additional transfers are allowed.)

0 = software initialization disabled

1 = software initialization enabled

A hardware reset sets this bit, enabling you to configure the RAM without

allowing any CAN bus activity. After a hardware reset or software initial-

ization, clearing this bit completes the initialization. The CAN peripheral

waits for a bus idle state (11 consecutive recessive bits) before partici-

pating in bus activities.

Software can set this bit to stop all receptions and transmissions on the

CAN bus. (To prevent transmission of a specific message object while its

contents are being updated, set the CPUUPD bit in the individual message

object’s control register 1. See “Configuring Message Objects” on page

7-20.)

Entering powerdown mode stops an in-progress CAN transmission

immediately. To avoid stopping a CAN transmission while it is sending a

dominant bit on the CAN bus, set the INIT bit before executing the IDLPD

instruction.

The CAN peripheral also sets this bit to isolate the CAN bus when an error

counter reaches 256. This isolation is called a

bus-off

condition. After a

bus-off condition, clearing this bit initiates a bus-off recovery sequence,

which clears the error counters. The CAN peripheral waits for 128 bus idle

states (128 packets of 11 consecutive recessive bits), then resumes

normal operation. (See “Bus-off State” on page 7-41.)

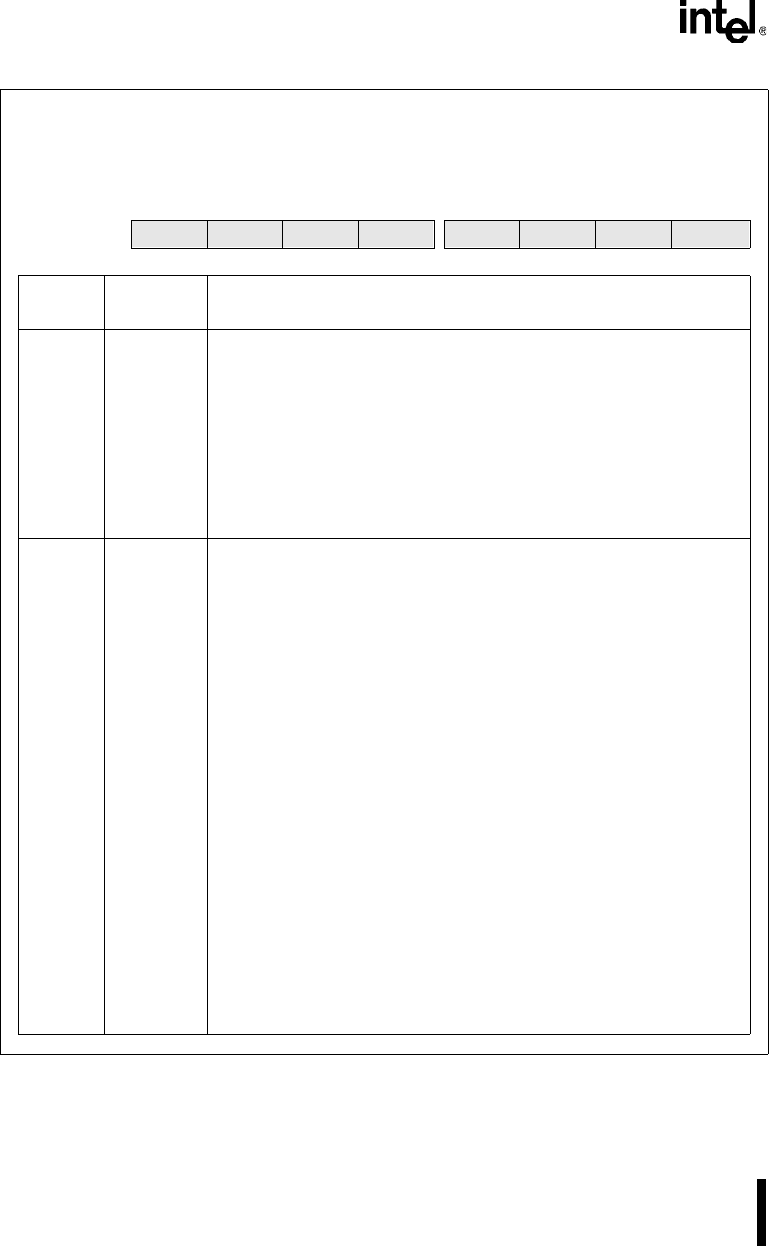

CAN_CON (Continued)

(87C196CB)

Address:

Reset State:

1E00H

01H

Program the CAN control (CAN_CON) register to control write access to the bit timing registers, to

enable and disable CAN interrupts, and to control access to the CAN bus.

7 0

87C196CB

— CCE — — EIE SIE IE INIT

Bit

Number

Bit

Mnemonic

Function

Figure 7-6. CAN Control (CAN_CON) Register (Continued)