87C196CB SUPPLEMENT

7-16

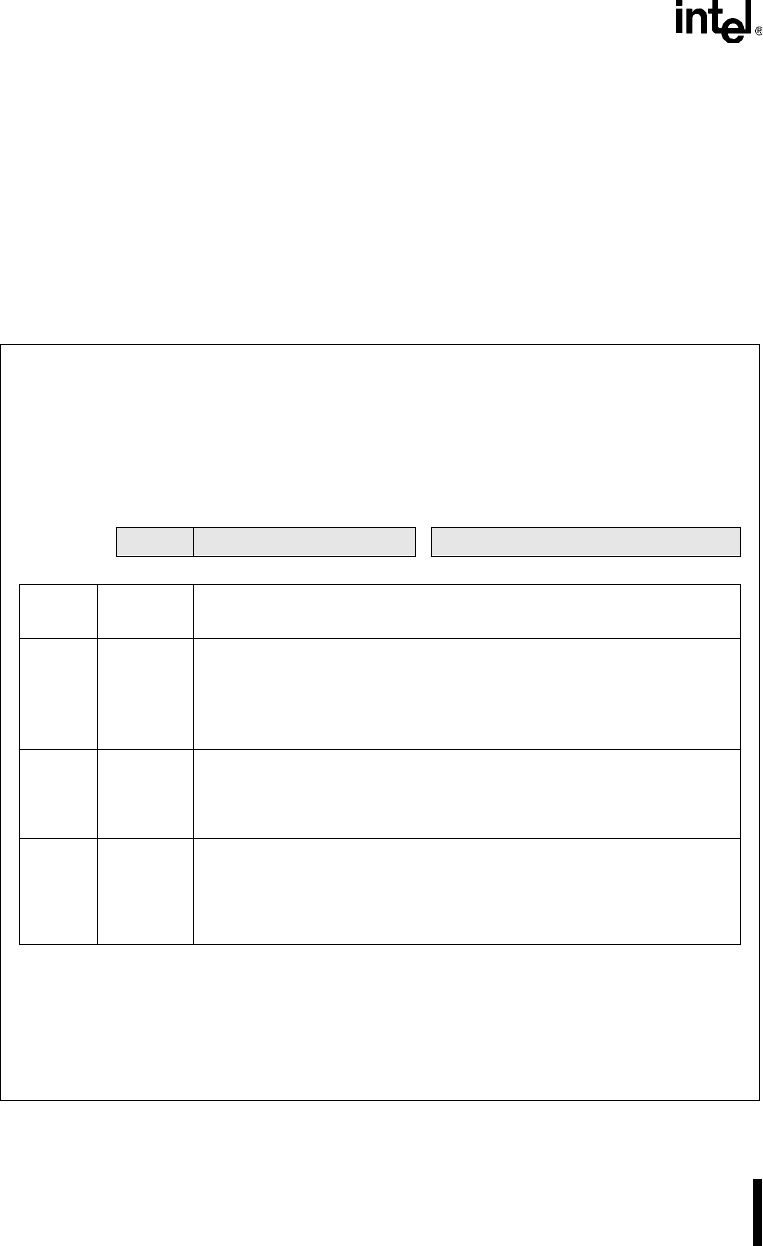

7.4.3 Programming the Bit Timing 1 (CAN_BTIME1) Register

Bit timing register 1 (Figure 7-8) controls the time at which the bus is sampled and the number

of samples taken. In single-sample mode, the bus is sampled once and the value of that sample is

considered valid. In three-sample mode, the bus is sampled three times and the value of the ma-

jority of those samples is considered valid. Single-sample mode may achieve a faster transmis-

sion rate, but it is more susceptible to errors caused by noise on the CAN bus. Three-sample mode

is less susceptible to noise-related errors, but it may be slower. If you specify three-sample mode,

the hardware adds two time quanta to the TSEG1 value to allow time for two additional samples

during t

TSEG1

.

CAN_BTIME1

†

(87C196CB)

Address:

Reset State:

1E4FH

Unchanged

Program the CAN bit timing 1 (CAN_BTIME1) register to define the sample time and the sample

mode. The CAN controller samples the bus during the last one (in single-sample mode) or three (in

three-sample mode) time quanta of t

TSEG1

, and initiates a transmission at the end of t

TSEG2

.

Therefore, specifying the lengths of t

TSEG1

and t

TSEG2

defines both the sample point and the trans-

mission point.

7 0

87C196CB

SPL TSEG2 TSEG1

Bit

Number

Bit

Mnemonic

Function

7 SPL Sampling Mode

This bit determines how many samples are taken to determine a valid bit

value.

0 = 1 sample

1 = 3 samples, using majority logic

6:4 TSEG2

††

Time Segment 2

This field determines the length of time that follows the sample point within

a bit time. Valid programmed values are 1–7; the hardware adds 1 to this

value.

3:0 TSEG1

††

Time Segment 1

This field defines the length of time that precedes the sample point within a

bit time. Valid programmed values are 2–15; the hardware adds 1 to this

value. In three-sample mode, the hardware adds 2 time quanta to allow

time for the two additional samples.

†

The CCE bit (CAN_CON.6) must be set to enable write access to this register.

††

For correct operation according to the CAN protocol, the total bit time must be at least 8 time

quanta, so the sum of the programmed values of TSEG1 and TSEG2 must be at least 5. (The

total bit time is the sum of t

SYNC_SEG

+ t

TSEG1

+ t

TSEG2

. The length of t

SYNC_SEG

is 1 time quanta,

and the hardware adds 1 to both TSEG1 and TSEG2. Therefore, if TSEG1 + TSEG2 = 5, the

total bit length will be equal to 8 (1+5+1+1)). Table 7-11 lists additional conditions that must be

met to maintain synchronization.

Figure 7-8. CAN Bit Timing 1 (CAN_BTIME1) Register