DE2-70 User Manual

42

JP1

1.8V

2.5V 3.3V

2

1

4

35

6

Figure 5.10. JP1 pin settings.

IO_A2

IO_A1

IO_A0

GP

IO_D0

GPIO_D1

IO_A10

IO_A20

IO_A24

IO_A28

IO_A6

IO_A

13

IO_A9

IO_A19

IO_A31

IO_A27

IO_A23

IO_A15

IO_A14

IO_A16

IO_A0

IO_A1

IO_A8

IO_A5

IO_A4

IO_A3

IO_A7

IO_A12

IO_A11

IO_A18

IO_A17

IO_A22

IO_A21

IO_A26

IO_A25

IO_A30

IO_A29

IO_CLKINp0

IO_CLKINn0

IO_CLKOUTp0

IO_CLKOUTn0

GPIO_

D1

GPIO_D0

VC

C

5

VCC33

VCCIO5

VCCIO5

(G

PIO 0)

D12

BAT54S

D12

BAT54S

1

2

3

R51

47

R51

47

D14

BAT54S

D14

BAT54S

1

2

3

J4

BOXH

eader

2X20M

J4

BOXH

eader

2X20M

1

2

3

4

5

6

7

8

9

10

11

13

12

14

16

18

20

22

24

26

27

15

17

19

21

23

25

28

29

31

33

35

37

39

30

32

34

36

38

40

R52

47

R52

47

(protection registors and diodes

not shown for other ports)

IO_B1

IO_B0

IO_B2

GPIO_D3

2

IO_B0

GPIO_D33

IO_B1

GPIO_D33

GPIO_D32

IO_B20

IO_B24

IO_B28

IO_B16

IO_B10

IO_B13

IO_B15

IO_B31

IO_B27

IO_B19

IO_B9

IO_B23

IO_B14

IO_B4

IO_B5

IO_

B8

IO_B6

IO_B3

IO_B7

IO_B12

I

O_B11

IO_B18

IO_B17

IO_B22

IO_B21

IO_B26

IO_B25

IO_B30

IO_B29

IO_CLKINp1

IO_CLKINn1

IO_CLKOUTp1

IO_CLKOUTn1

VCC33

VCC5

VCC

IO5

VCCIO5

(GPIO 1)

D50

BAT54S

D50

BAT54S

1

2

3

J5

BOXHeader 2X

20M

J5

BOXHeader 2X

20M

1

2

3

4

5

6

7

8

9

10

11

13

12

14

16

18

20

22

24

26

27

15

17

19

21

23

25

28

29

31

3

3

35

37

39

30

32

34

36

38

40

R60

47

R60

47

D48

BAT54S

D48

BAT54S

1

2

3

R61

47

R61

47

(protection registors and diodes

not shown for other ports)

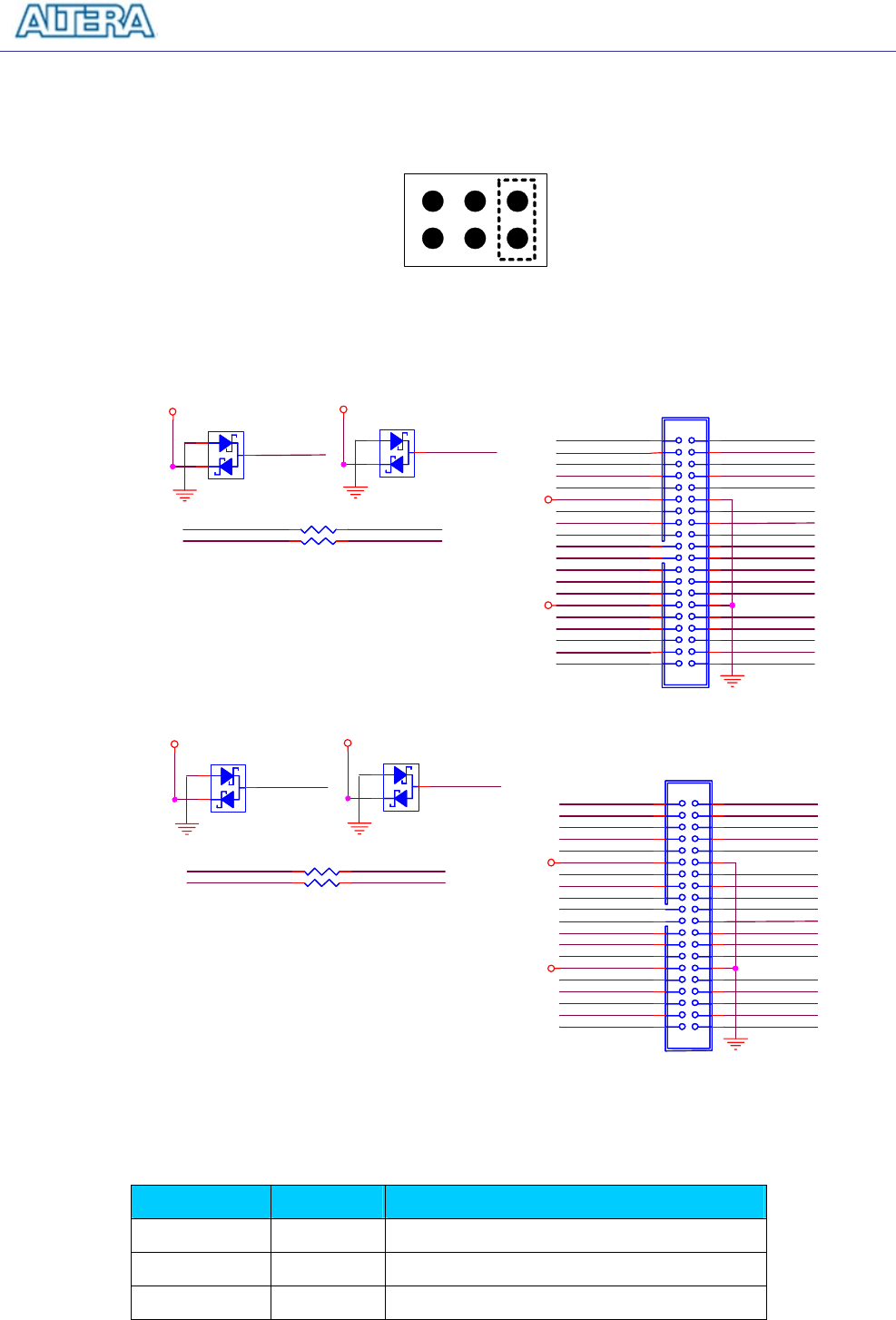

Figure 5.11. Schematic diagram of the expansion headers.

Signal Name FPGA Pin No. Description

IO_A [0] PIN_C30 GPIO Connection 0 IO[0]

IO_A [1] PIN_C29 GPIO Connection 0 IO[1]

IO_A [2] PIN_E28 GPIO Connection 0 IO[2]