DE2-70 User Manual

62

DRAM1_RAS_N PIN_N9 SDRAM 2 Row Address Strobe

DRAM1_CAS_N PIN_N8 SDRAM 2 Column Address Strobe

DRAM1_CKE PIN_L10 SDRAM 2 Clock Enable

DRAM1_CLK PIN_G5 SDRAM 2 Clock

DRAM1_WE_N PIN_M9 SDRAM 2 Write Enable

DRAM1_CS_N PIN_P9 SDRAM 2 Chip Select

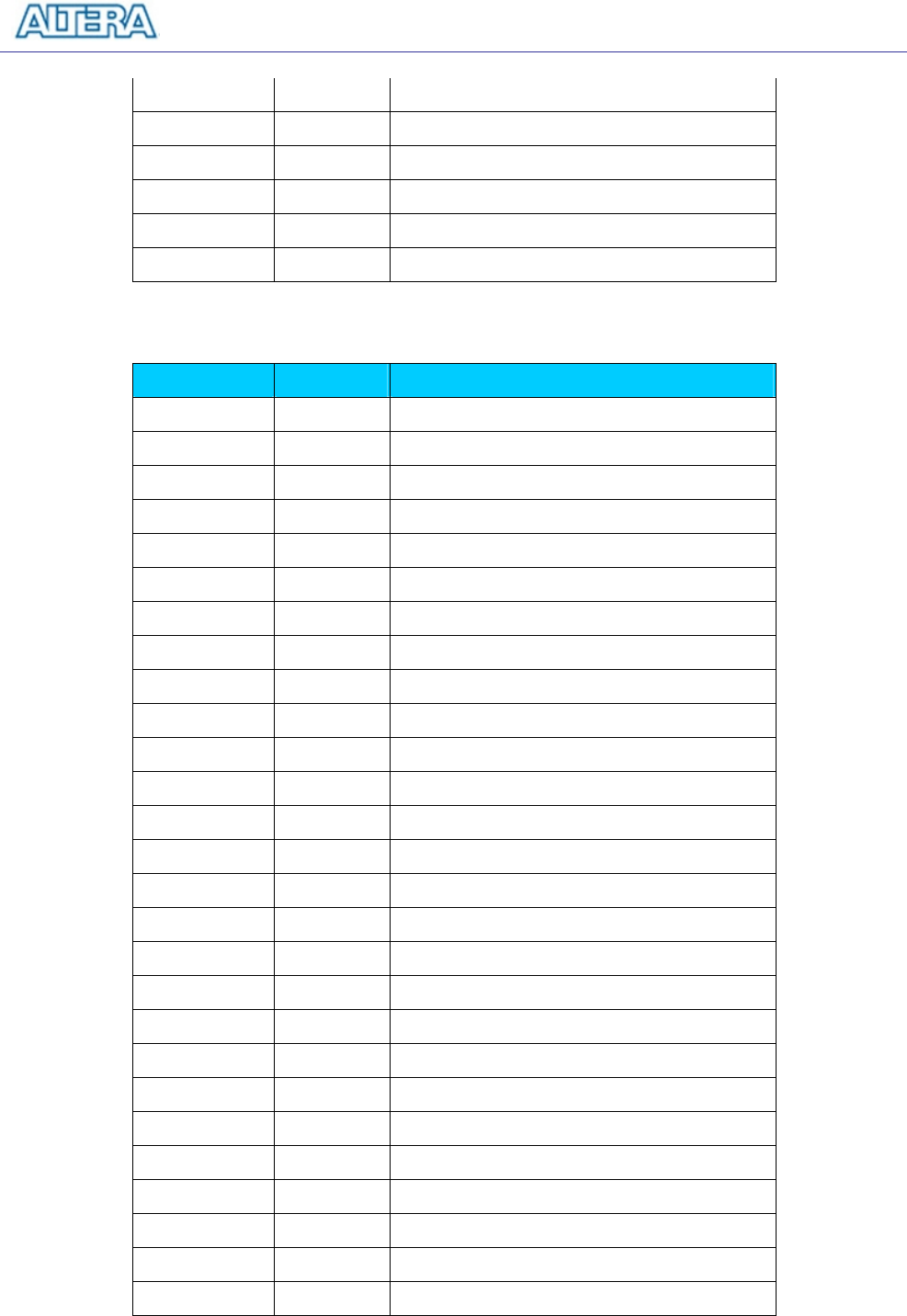

Table 5.19. SDRAM pin assignments.

Signal Name FPGA Pin No. Description

SRAM_A[0] PIN_AG8 SRAM Address[0]

SRAM_A[1] PIN_AF8 SRAM Address[1]

SRAM_A[2] PIN_AH7 SRAM Address[2]

SRAM_A[3] PIN_AG7 SRAM Address[3]

SRAM_A[4] PIN_AG6 SRAM Address[4]

SRAM_A[5] PIN_AG5 SRAM Address[5]

SRAM_A[6] PIN_AE12 SRAM Address[6]

SRAM_A[7] PIN_AG12 SRAM Address[7]

SRAM_A[8] PIN_AD13 SRAM Address[8]

SRAM_A[9] PIN_AE13 SRAM Address[9]

SRAM_A[10] PIN_AF14 SRAM Address[10]

SRAM_A[11] PIN_AG14 SRAM Address[11]

SRAM_A[12] PIN_AE15 SRAM Address[12]

SRAM_A[13] PIN_AF15 SRAM Address[13]

SRAM_A[14] PIN_AC16 SRAM Address[14]

SRAM_A[15] PIN_AF20 SRAM Address[15]

SRAM_A[16] PIN_AG20 SRAM Address[16]

SRAM_A[17] PIN_AE11 SRAM Address[17]

SRAM_A[18] PIN_AF11 SRAM Address[18]

SRAM_DQ[0] PIN_AH10 SRAM Data[0]

SRAM_DQ[1] PIN_AJ10 SRAM Data[1]

SRAM_DQ[2] PIN_AK10 SRAM Data[2]

SRAM_DQ[3] PIN_AJ11 SRAM Data[3]

SRAM_DQ[4] PIN_AK11 SRAM Data[4]

SRAM_DQ[5] PIN_AH12 SRAM Data[5]

SRAM_DQ[6] PIN_AJ12 SRAM Data[6]

SRAM_DQ[7] PIN_AH16 SRAM Data[7]