DE2-70 User Manual

59

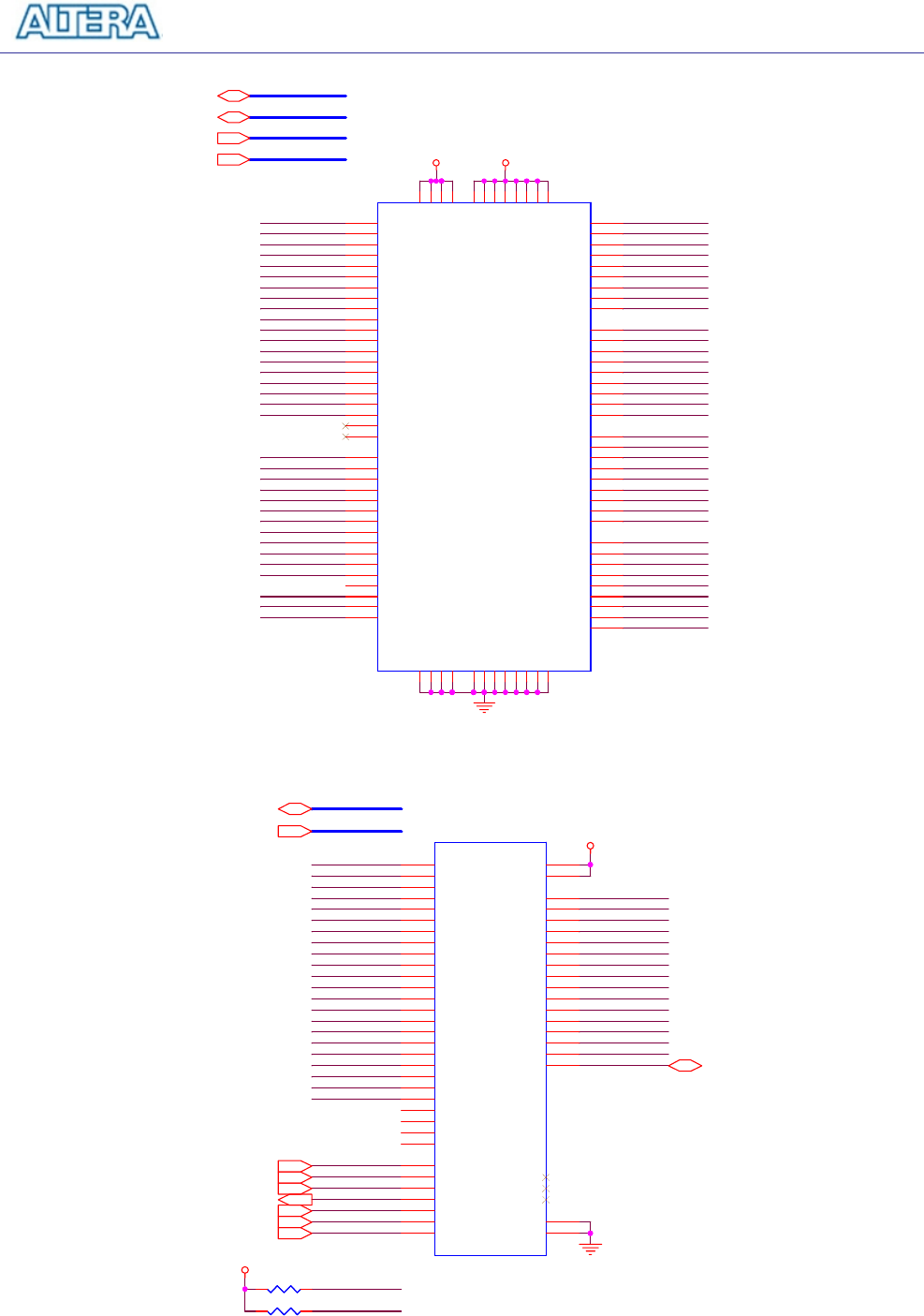

SRAM_byteen_n1

SRAM_byteen_n2

SRAM_byteen_n3

SRAM_addr7

SRAM_addr8

SRAM_addr9

SRAM_addr10

SRAM_addr11

SRAM_addr12

SRAM_addr13

SRAM_addr14

SRAM_addr15

SRAM_addr16

SRAM_addr17

SRAM_addr18

SRAM_addr0

SRAM_addr1

SRAM_addr2

SRAM_addr3

SRAM_addr4

SRAM_addr5

SRAM_addr6

SRAM_byteen_n0

SRAM_ZZ

SRAM_MODE

SRAM_chipen2

SRAM_chipen3_n

SRAM_outen_n

SRAM_clock

SRAM_globalw_n

SRAM_writeen_n

SRAM_advance_n

SRAM_adsconttroler_n

SRAM_adsprocessor_n

SRAM_chipen1_n

SRAM_data24

SRAM_datapar0

SRAM_datapar1

SRAM_data4

SRAM_data5

SRAM_data6

SRAM_data7

SRAM_datapar2

SRAM_data8

SRAM_data9

SRAM_data10

SRAM_data11

SRAM_data12

SRAM_data13

SRAM_data14

SRAM_data15

SRAM_data18

SRAM_data19

SRAM_data20

SRAM_data21

SRAM_data22

SRAM_data23

SRAM_data25

SRAM_data26

SRAM_data31

SRAM_data27

SRAM_data28

SRAM_data29

SRAM_data0

SRAM_data30

SRAM_data1

SRAM_data2

SRAM_data3

SRAM_datapar3

SRAM_data16

SRAM_data17

SRAM_DQ[0..31]

SRAM_DPA[0..3]

SRAM_A[0..18]

SRAM_BE_n[0..3]

SR_VCC33SR_VCC33

IS61LPS51236A-200TQLI

U3

SSRAM 512Kx36

U3

SSRAM 512Kx36

DQPC

1

DQC0

2

DQC1

3

VDDQ

4

VSSQ

5

DQC2

6

DQC3

7

DQC4

8

DQC5

9

VSSQ

10

VDDQ

11

DQC6

12

DQC7

13

VDD

15

VSS

17

DQD0

18

DQD1

19

VDDQ

20

VSSQ

21

DQD2

22

DQD3

23

DQD4

24

DQD5

25

VSSQ

26

VDDQ

27

DQD6

28

DQD7

29

DQPD

30

MODE

31

A5

32

A4

33

A3

34

A2

35

A1

36

A0

37

NC/A19

39

NC/A20

38

VSS

40

VDD

41

A6

44

A7

45

A8

46

A9

47

A10

48

A11

49

A12

50

A13

81

A14

82

DQPA

51

DQA0

52

DQA1

53

VDDQ

54

VSSQ

55

DQA2

56

DQA3

57

DQA4

58

DQA5

59

VSSQ

60

VDDQ

61

DQA6

62

DQA7

63

ZZ

64

VDD

65

VSS

67

DQB0

68

DQB1

69

VDDQ

70

VSSQ

71

DQB2

72

DQB3

73

DQB4

74

DQB5

75

VSSQ

76

VDDQ

77

DQB6

78

DQB7

79

DQPB

80

A15

99

A16

100

ADV_n

83

ADSP_n

84

ADSC_n

85

OE_n

86

BWE_n

87

GW_n

88

CLK

89

VSS

90

VDD

91

CE3_n

92

BWA_n

93

BWB_n

94

BWC_n

95

BWD_n

96

CE2

97

CE1_n

98

A17

43

A18

42

Figure 5.23. SSRAM schematic.

FLASH_A1

FLASH_A17

FLASH_A20

FLASH_A16

FLASH_A15

FLASH_A14

FLASH_A13

FLASH_A12

FLASH_A11

FLASH_A10

FLASH_A9

FLASH_A19

FLASH_A18

FLASH_A8

FLASH_A7

FLASH_A6

FLASH_A5

FLASH_A4

FLASH_A3

FLASH_A2

FLASH_A21

FLASH_CE_n

FLASH_RY

FLASH_D7

FLASH_D6

FLASH_D5

FLASH_D4

FLASH_D3

FLASH_D2

FLASH_D1

FLASH_D0

FLASH_D14

FLASH_D13

FLASH_D12

FLASH_D11

FLASH_D10

FLASH_D8

FLASH_D9

FLASH_A0

FLASH_D[0..14]

FLASH_D15_A-1

FLASH_A[0..21]

FLASH_CE_n

FLASH_OE_n

FLASH_WE_n

FLASH_RESET_n

FLASH_WP_n

FLASH_BYTE_n

FLASH_RY

F_VCC33

F_VCC33

R33 4.7KR33 4.7K

U5

FLASH 8Mx8

U5

FLASH 8Mx8

A15

3

A14

4

A13

5

A12

6

A11

7

A10

8

A9

9

A8

10

A19

11

A20

12

WE#

13

RESET#

14

A21

15

WP#ACC

16

RY/BY#

17

A18

18

A17

19

A7

20

A6

21

A5

22

A4

23

A3

24

A2

25

A1

26

A16

54

BYTE#

53

VSS

52

DQ15/A-1

51

DQ7

50

DQ14

49

DQ6

48

DQ13

47

DQ5

46

DQ12

45

DQ4

44

VCC

43

DQ11

42

DQ3

41

DQ10

40

DQ2

39

DQ9

38

DQ1

37

DQ8

36

DQ0

35

OE#

34

VSS

33

CE#

32

A0

31

A22

2

A23

1

A24

56

A25

55

VIO

29

RFU0

27

RFU1

28

RFU2

30

R32 4.7KR32 4.7K

Figure 5.24. Flash schematic.