DE2-70 User Manual

55

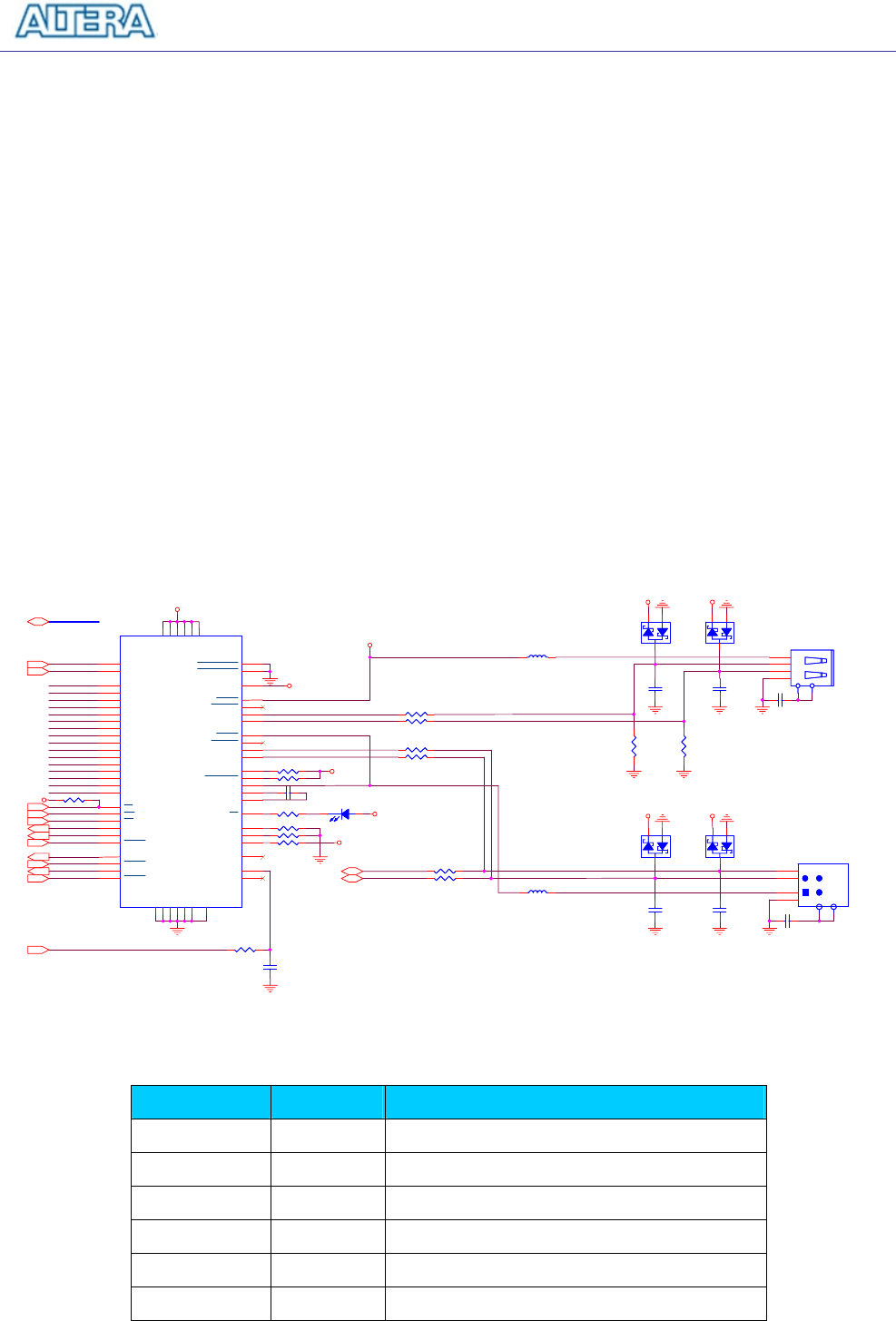

5.14 Using USB Host and Device

The DE2-70 board provides both USB host and device interfaces using the Philips ISP1362

single-chip USB controller. The host and device controllers are compliant with the Universal Serial

Bus Specification Rev. 2.0, supporting data transfer at full-speed (12 Mbit/s) and low-speed (1.5

Mbit/s). Figure 5.20 shows the schematic diagram of the USB circuitry; the pin assignments for the

associated interface are listed in Table 5.17.

Detailed information for using the ISP1362 device is available in its datasheet and programming

guide; both documents can be found on the manufacturer’s web site, or in the Datasheet/USB folder

on the DE2-70 System CD-ROM. The most challenging part of a USB application is in the design

of the software driver needed. Two complete examples of USB drivers, for both host and device

applications, can be found in Sections 6.4 and 6.5. These demonstrations provide examples of

software drivers for the Nios II processor.

OTG_D15

OTG_D14

OTG_D13

OTG_D12

OTG_D11

OTG_D10

OTG_D9

OTG_D8

OTG_D7

OTG_D6

OTG_D4

OTG_D5

OTG_D3

OTG_D2

OTG_D0

OTG_D1

O_VCC5

H_VCC5

OTG_D[0..15]

OTG_FSPEED

OTG_LSPEED

OTG_WE_n

OT

G_OE_n

OTG_RESET_n

OTG_DA

CK0_n

OTG_DACK1_n

OTG_CS_n

OTG_A1

OTG_A0

12MHZ

OTG_INT1

OTG_INT0

OTG_DREQ1

O

TG_DREQ0

U_VCC33

U_VCC33

U_VCC33

U_VCC33

U_VCC5

U_VCC5

O_VCC5

O_V

CC5

H_VCC5

H_VCC5

U_VCC33

BC66 0.1uBC66 0.1u

R120

330

R120

330

C54

47p

C54

47p

J13

USB A

-TYPE

J13

USB A

-TYPE

1

2

3

4

5

6

L10

BEAD

L10

BEAD

R115

15K

R115

15K

C53

47p

C53

47p

R111

4.7K

R111

4.7K

R118

4.7K

R118

4.7K

D88

BAT54S

D88

BAT54S

1

2

3

D85

BAT54S

D85

BAT54S

1

2

3

R126

22

R126

22

D86

BAT54S

D86

BAT54S

1

2

3

R119

4.7K

R119

4.7K

C52

47p

C52

47p

R112

22

R112

22

U14

ISP1362

U14

ISP1362

D6

7

INT2

31

INT1

30

D10

12

D2

2

D3

3

CS

21

WR

22

TEST0

23

DREQ1

24

DR

EQ2

25

VCC

26

DGND

27

DACK1

28

D14

17

D15

18

DGND

19

RD

20

D13

16

D12

15

VCC

14

D11

13

DACK2

29

RESET

32

DGND

1

VCC

4

D9

11

D8

10

D4

5

D5

6

D7

8

DGND

9

H_SUSPEN

D/H_SUSW

KUP

33

H_SUSPEND/D_SUSW

KUP

34

H_PSW

1

35

H_PSW

2

36

DGND

37

CLKOUT

38

GL

39

VCC

40

H_OC2

41

H_OC1

42

X1

43

X2

44

OTGMODE

45

H_DM2

46

H_DP2

47

ID

48

OTG_DM1

49

OTG_DP1

50

AGND

51

VCC

52

CP_CAP1

53

CP_CAP2

54

VBUS

55

VDD_5V

56

DGND

57

VCC

58

TEST1

59

TEST2

60

A0

61

A1

62

D0

63

D1

64

BC68 0.1uBC68 0.1u

R125

1.5K

R125

1.5K

R124

1.5K

R124

1.5K

C48

47p

C48

47p

R113

22

R113

22

R114

15K

R114

15K

GOOD

LEDB

GOOD

LEDB

R121

10K

R121

10K

R116

22

R116

22

R117

22

R117

22

VBU S

GND

D- D+

J14

USB B-TYPE

VBU S

GND

D- D+

J14

USB B-TYPE

4

3

2

1

5

6

C49

47p

C49

47p

R122

10K

R122

10K

C50 0.1uC50 0.1u

D87

BAT54S

D87

BAT54S

1

2

3

R123

100K

R123

100K

L11

BEAD

L11

BEAD

Figure 5.20. USB (ISP1362) host and device schematic.

Signal Name FPGA Pin No. Description

OTG_A[0] PIN_E9 ISP1362 Address[0]

OTG_A[1] PIN_D8 ISP1362 Address[1]

OTG_D[0] PIN_H10 ISP1362 Data[0]

OTG_D[1] PIN_G9 ISP1362 Data[1]

OTG_D[2] PIN_G11 ISP1362 Data[2]

OTG_D[3] PIN_F11 ISP1362 Data[3]