DE2-70 User Manual

58

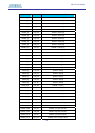

DRAM0_A3

DRAM0_A0

DRAM0_A2

DRAM0_A1

DRAM0_A10

DRAM_D5

DRAM_D0

DRAM_D7

DRAM_D6

DRAM_D3

DRAM_D2

DRAM_D4

DRAM_D1

DRAM1_A3

DRAM1_A0

DRAM1_A2

DRAM1_

A1

DRAM1_A10

DRAM_D21

DRAM_D16

DRAM_D23

DRAM_D22

DRAM_D19

DRAM_D18

DRAM_D20

DRAM_D17

DRAM1_A12

DRAM1_A5

DRAM1_A7

DRAM1_A6

DRAM1_A8

DRAM1_A11

DRAM1_A4

DRAM1_A9

DRAM_D

24

DRAM_D31

DRAM_D27

DRAM_D25

DRAM_D26

DRAM_D29

DRAM_D30

DR

AM_D28

DRAM0_A12

DRAM0_A5

DRAM0_A7

DRAM0_

A6

DRAM0_A8

DRAM0_A11

DRAM0_A4

DRAM0_A9

DRAM_D8

DRAM_D15

DRAM_D11

DRAM_D9

DRAM_D10

DRAM_D

13

DRAM_D14

DRAM_D12

DRAM0_CKE

DRAM0_CAS_n

DRAM0_RAS_n

DRAM0_CS_n

DRAM1_CKE

DRAM1_CAS_n

DRAM1_RAS_n

DRAM1_CS

_n

DRAM1_WE_n

DRAM0_WE_n

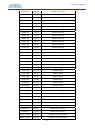

DR

A

M_D[0..31]

DRAM0_A[0..12]

DRAM0_LDQM0

DRAM0_UDQM1

DRAM0_CLK

DRAM0_CKE

DRAM0_BA0

DRAM0_BA1

DRAM0_WE_n

DRAM0_CAS_n

DRAM0_

RAS_n

DRAM0_CS_n

DRAM1_L

DQM0

DRAM1_UDQM1

DRAM1_CLK

DRAM1_CKE

DRAM1_BA0

DRAM1_BA1

DRAM1_WE_n

DRAM1_CAS_n

DRAM1_RAS_n

DRAM1_CS_n

DRAM1_A[0..12]

DR_VCC33

DR_VCC33

DR_VCC33

SDRAM0

SDRAM1

U2

SDRAM 16Mx16

U2

SDRAM 16Mx16

A0

23

A1

24

A2

25

A3

26

A4

29

A5

30

A6

31

A7

32

A8

33

A9

34

nCAS

17

nRAS

18

LDQM

15

nWE

16

nCS

19

CKE

37

CLK

38

UDQM

39

D0

2

D1

4

D2

5

D3

7

D4

8

D5

10

D6

11

D7

13

D8

42

D9

44

D10

45

D11

47

D12

48

D13

50

D14

51

D15

53

A12

36

BA0

20

VDD

1

VDD

27

VSS

28

VSS

41

A10

22

VDDQ

3

VDDQ

9

VDDQ

43

VDDQ

49

VSSQ

6

VSSQ

12

VSSQ

46

VSSQ

52

A11

35

BA1

21

VSS

54

VDD

14

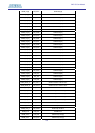

R1

4.7K

R1

4.7K

U1

SDRAM 16Mx16

U1

SDRAM 16Mx16

A0

23

A1

24

A2

25

A3

26

A4

29

A5

30

A6

31

A7

32

A8

33

A9

34

nCAS

17

nRAS

18

LDQM

15

nWE

16

nCS

19

CKE

37

CLK

38

UDQM

39

D0

2

D1

4

D2

5

D3

7

D4

8

D5

10

D6

11

D7

13

D8

42

D9

44

D10

45

D11

47

D12

48

D13

50

D14

51

D15

53

A12

36

BA0

20

VDD

1

VDD

27

VSS

28

VSS

41

A10

22

VDDQ

3

VDDQ

9

VDDQ

43

VDDQ

49

VSSQ

6

VSSQ

12

VSSQ

46

VSSQ

52

A11

35

BA1

21

VSS

54

VDD

14

R4

4.7K

R4

4.7K

R3

4.7K

R3

4.7K

R9

4.7K

R9

4.7K

R5

4.7K

R5

4.7K

R10

4.7K

R10

4.7K

R8

4.7K

R8

4.7K

R2

4.7K

R2

4.7K

R11

4.7K

R11

4.7K

R7

4.7K

R7

4.7K

DR_VCC33

Figure 5.22. SDRAM schematic.