104 EPSON S1C63000 CORE CPU MANUAL

CHAPTER 4: INSTRUCTION SET

LD [%ir],[%ir’]+

Load location [ir’ reg.] into location [ir reg.] and increment ir’ reg. 2 cycles

Function: [ir] ← [ir’], ir’ ← ir’ + 1

Loads the content of the data memory addressed by the ir’ register (X or Y) into the data

memory addressed by the ir register (Y or X). Then increments the ir’ register (Y or X).

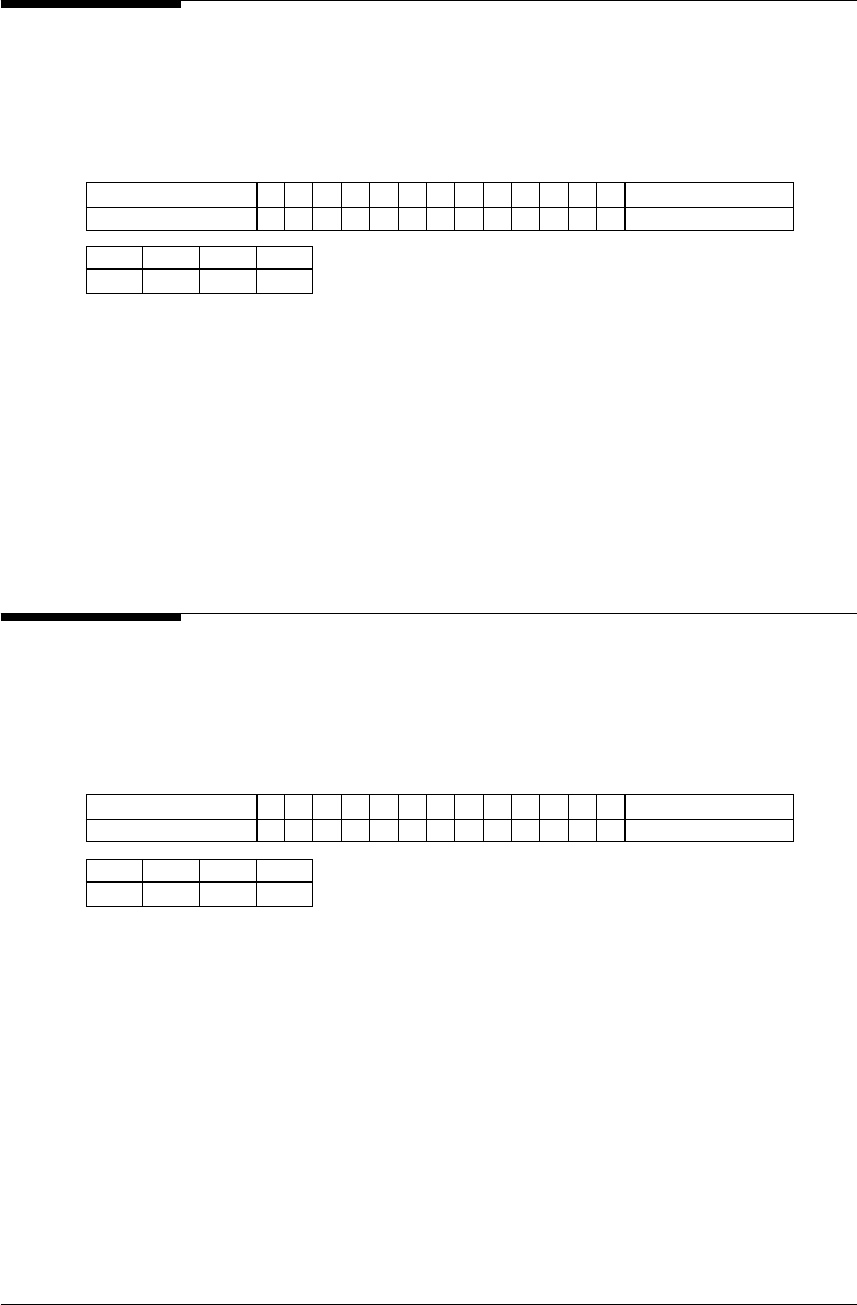

Code:

Mnemonic MSB LSB

LD [%X],[%Y]+ 11110111110111EFBH

LD [%Y],[%X]+ 11110111110011EF9H

Flags: EICZ

↓ –––

Mode: Src: Register indirect

Dst: Register indirect

Extended addressing: Invalid

LD [%ir]+,[%ir’] Load location [ir’ reg.] into location [ir reg.] and increment ir reg. 2 cycles

Function: [ir] ← [ir’], ir ← ir + 1

Loads the content of the data memory addressed by the ir’ register (X or Y) into the data

memory addressed by the ir register (Y or X). Then increments the ir register (X or Y).

Code:

Mnemonic MSB LSB

LD [%X]+,[%Y] 11110111111101EFEH

LD [%Y]+,[%X] 11110111111001EFCH

Flags: EICZ

↓ –––

Mode: Src: Register indirect

Dst: Register indirect

Extended addressing: Invalid