66 EPSON S1C63000 CORE CPU MANUAL

CHAPTER 4: INSTRUCTION SET

ADC %B,[%ir]+,n4

ADC [%ir],%B,n4 Add with carry B reg. to location [ir reg.] in specified radix 2 cycles

Function: [ir] ← N's adjust ([ir] + B + C)

Adds the content of the B register and carry (C) to the data memory addressed by the ir

register (X or Y). The operation result is adjusted with n4 as the radix. The C flag is set by a

carry according to the radix.

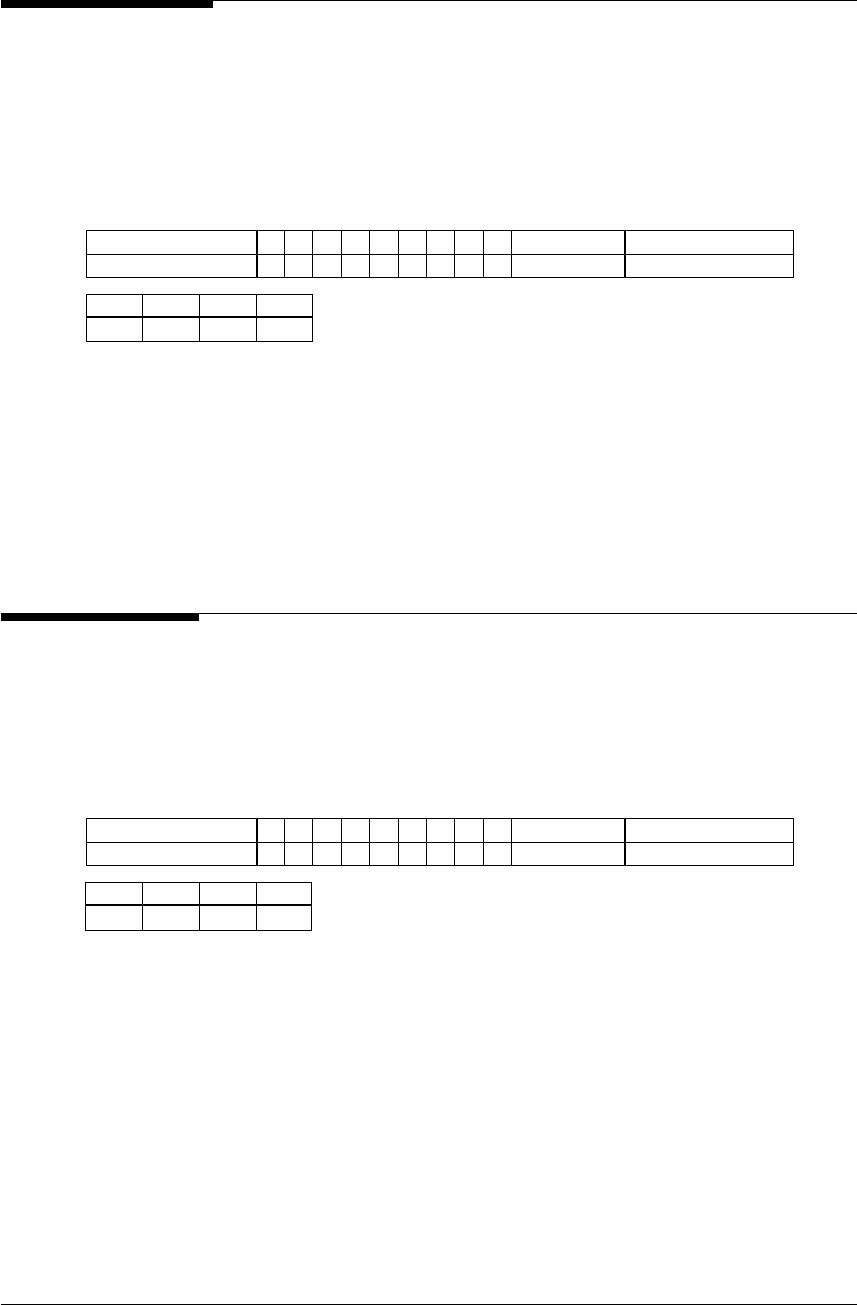

Code:

Mnemonic MSB LSB

ADC [%X],%B,n4 111010100 [10H-n4] 1D40H–1D4FH

ADC [%Y],%B,n4 111010110 [10H-n4] 1D60H–1D6FH

Flags: EICZ

↓ – ↕↕

Mode: Src: Register direct

Dst: Register indirect

Extended addressing: Valid

Extended LDB %EXT,imm8

operation: ADC [%X],%B,n4 [00imm8] ← N’s adjust ([00imm8] + B + C)

(00imm8 = 0000H + 00H to FFH)

LDB %EXT,imm8

ADC [%Y],%B,n4 [FFimm8] ← N’s adjust ([FFimm8] + B + C)

(FFimm8 = FF00H + 00H to FFH)

Note: n4 should be specified with a value from 1 to 16.

Add with carry location [ir reg.] to B reg. in specified radix and increment ir reg. 2 cycles

Function: B ← N's adjust (B + [ir] + C), ir ← ir + 1

Adds the content of the data memory addressed by the ir register (X or Y) and carry (C) to the

B register. The operation result is adjusted with n4 as the radix. Then increments the ir register

(X or Y). The flags change due to the operation result of the B register and the increment result

of the ir register does not affect the flags. The C flag is set by a carry according to the radix.

Code:

Mnemonic MSB LSB

ADC %B,[%X]+,n4 111011101 [10H-n4] 1DD0H–1DDFH

ADC %B,[%Y]+,n4 111011111 [10H-n4] 1DF0H–1DFFH

Flags: EICZ

↓ – ↕↕

Mode: Src: Register indirect

Dst: Register direct

Extended addressing: Invalid

Note: n4 should be specified with a value from 1 to 16.