S1C63000 CORE CPU MANUAL EPSON 71

CHAPTER 4: INSTRUCTION SET

ADD [%ir]+,%r Add r reg. to location [ir reg.] and increment ir reg. 2 cycles

Function: [ir] ← [ir] + r, ir ← ir + 1

Adds the content of the r register (A or B) to the data memory addressed by the ir register (X or

Y). Then increments the ir register (X or Y). The flags change due to the operation result of the

data memory and the increment result of the ir register does not affect the flags.

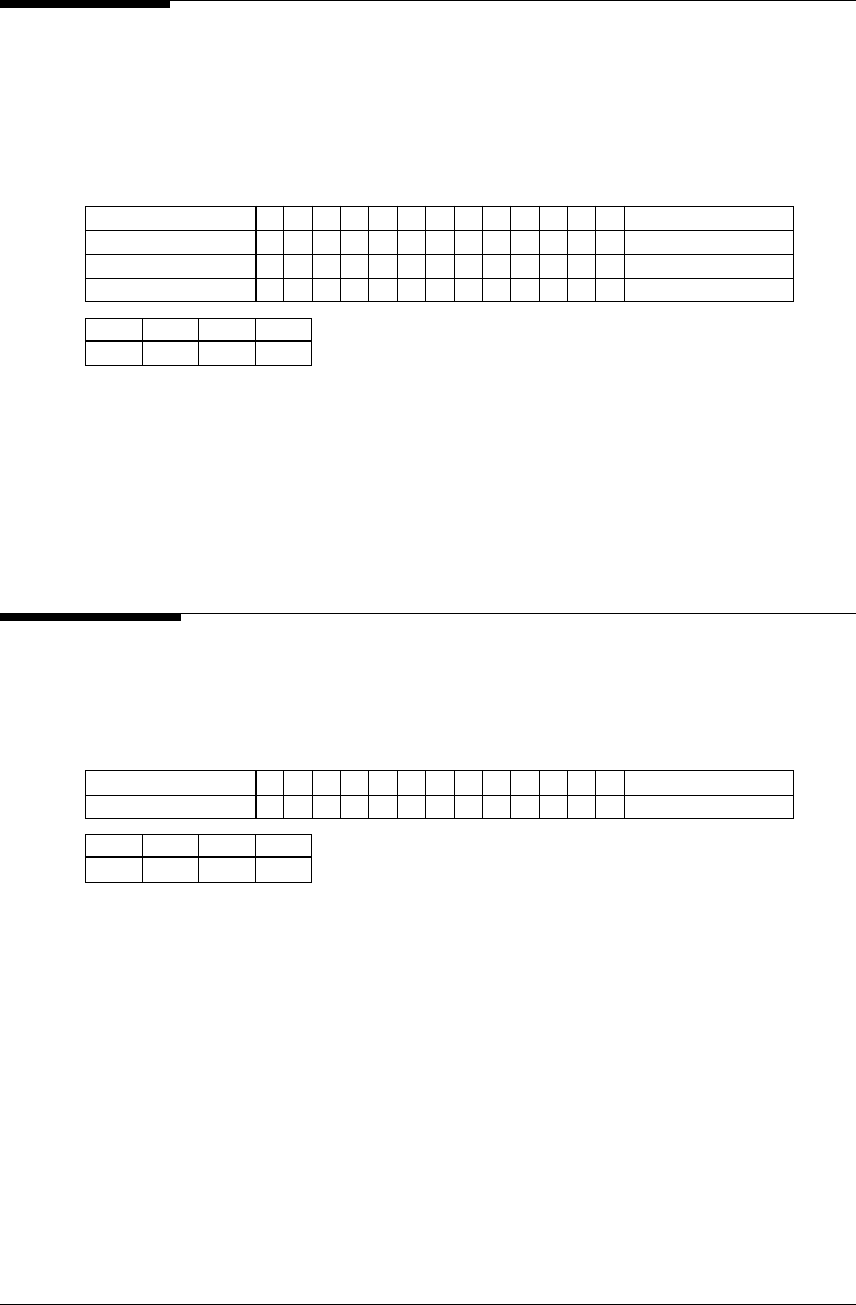

Code:

Mnemonic MSB LSB

ADD [%X]+,%A 11001011010011969H

ADD [%X]+,%B 1100101101101196DH

ADD [%Y]+,%A 1100101101011196BH

ADD [%Y]+,%B 1100101101111196FH

Flags: EICZ

↓ – ↕↕

Mode: Src: Register direct

Dst: Register indirect

Extended addressing: Invalid

ADD [%ir],imm4 Add immediate data imm4 to location [ir reg.] 2 cycles

Function: [ir] ← [ir] + imm4

Adds the 4-bit immediate data imm4 to the data memory addressed by the ir register (X or Y).

Code: Mnemonic MSB LSB

ADD [%X],imm4 110010000i3i2i1i01900H–190FH

ADD [%Y],imm4 110010010i3i2i1i01920H–192FH

Flags: EICZ

↓ – ↕↕

Mode: Src: Immediate data

Dst: Register indirect

Extended addressing: Valid

Extended LDB %EXT,imm8

operation: ADD [%X],imm4 [00imm8] ← [00imm8] + imm4 (00imm8 = 0000H + 00H to FFH)

LDB %EXT,imm8

ADD [%Y],imm4 [FFimm8] ← [FFimm8] + imm4 (FFimm8 = FF00H + 00H to FFH)