S1C63000 CORE CPU MANUAL EPSON 59

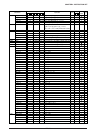

CHAPTER 4: INSTRUCTION SET

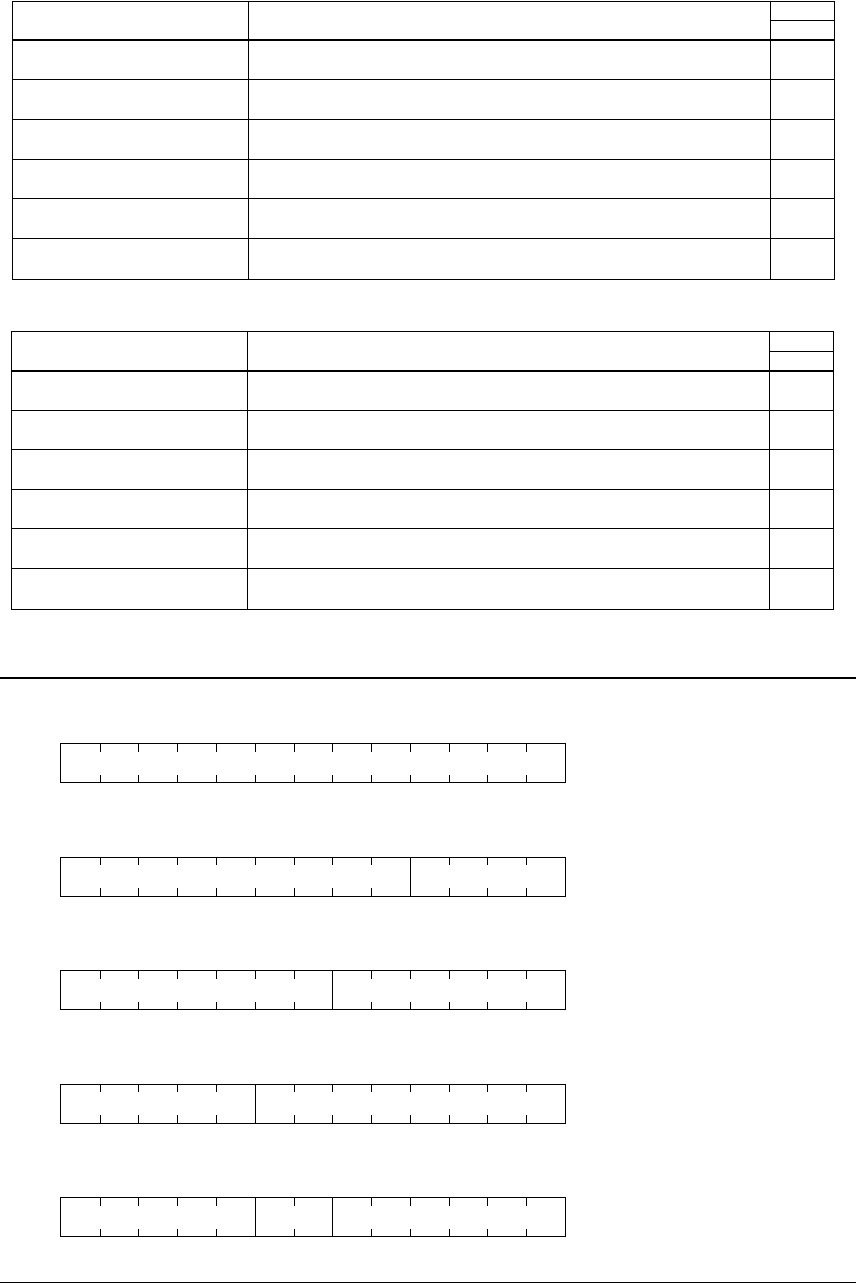

4.3 Instruction Formats

All the instructions of the S1C63000 are configured with 1 word (13 bits) as follows:

I

OP Code

Examples:

LD

ADD

PUSH

%A,%B

%A,[%X]

%F

II

OP Code

Examples:

LD

ADC

BIT

%A,imm4

[%Y],%B,n4

%B,imm4

III

OP Code

Examples:

INC

CALR

INT

[addr6]

[addr6]

imm6

IV

OP Code

Examples:

LDB

CALZ

JR

%BA,imm8

imm8

sign8

V

OP Code

Examples:

CLR

SET

TST

[addr6],imm2

[addr6],imm2

[addr6],imm2

Operand

Operand

Operand

Operand Operand

13-bit operation code

9-bit operation code + 4-bit immediate data

7-bit operation code + 6-bit immediate data

5-bit operation code + 8-bit immediate data

5-bit operation code + 2-bit immediate data + 6-bit immediate data

↓ –––

↓ –––

↓ –––

↓ –––

↓ –––

↓ –––

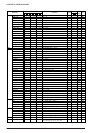

(sign16 : imm8 is upper 8-bit, sign8 is lower 8-bit)

PC ← PC + sign16 + 1 (sign16 = 32767~-32768)

If C = 1 then

PC ← PC + sign16 + 1 (sign16 = 32767 ~ -32768)

If C = 0 then

PC ← PC + sign16 + 1 (sign16 = 32767 ~ -32768)

If Z = 1 then

PC ← PC + sign16 + 1 (sign16 = 32767 ~ -32768)

If Z = 0 then

PC ← PC + sign16 + 1 (sign16 = 32767 ~ -32768)

( [SP1 - 1 ∗4 + 3] ~ [ (SP1 - 1) ∗4] ) ← PC + 1, SP1 ← SP1 - 1

PC ← PC + sign16 + 1 (sign16 = 32767 ~ -32768)

Mnemonic Operation

Flag

EICZ

signed 16-bit PC relative addressing

LDB %EXT,imm8

JR sign8

LDB %EXT,imm8

JRC sign8

LDB %EXT,imm8

JRNC sign8

LDB %EXT,imm8

JRZ sign8

LDB %EXT,imm8

JRNZ sign8

LDB %EXT,imm8

CALR sign8

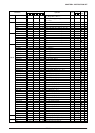

↓ –––

↓ –––

↓ ––

↓ ––

↓ –

↓ –

X ← imm16 (∗1 is upper 8-bit, ∗2 is lower 8-bit)

Y ← imm16 (∗1 is upper 8-bit, ∗2 is lower 8-bit)

X ← X + imm16 (∗1 is upper 8-bit, ∗2 is lower 8-bit)

Y ← Y + imm16 (∗1 is upper 8-bit, ∗2 is lower 8-bit)

X - imm16 (FFH - ∗1 is upper 8-bit, ∗2 is lower 8-bit)

Y - imm16 (FFH - ∗1 is upper 8-bit, ∗2 is lower 8-bit)

Mnemonic Operation

Flag

EICZ

16-bit immediate data addressing

LDB %EXT,imm8 ∗1

LDB %XL,imm8 ∗2

LDB %EXT,imm8 ∗1

LDB %YL,imm8 ∗2

LDB %EXT,imm8 ∗1

ADD %X,sign8 ∗2

LDB %EXT,imm8 ∗1

ADD %Y,sign8 ∗2

LDB %EXT,imm8 ∗1

CMP %X,imm8 ∗2

LDB %EXT,imm8 ∗1

CMP %X,imm8 ∗2

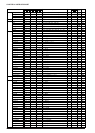

↔

↔

↔

↔↔↔