90 EPSON S1C63000 CORE CPU MANUAL

CHAPTER 4: INSTRUCTION SET

DEC %sp

EX %A,%B Exchange A reg. and B reg. 1 cycle

Function: A ↔ B

Exchanges the contents of the A register and B register.

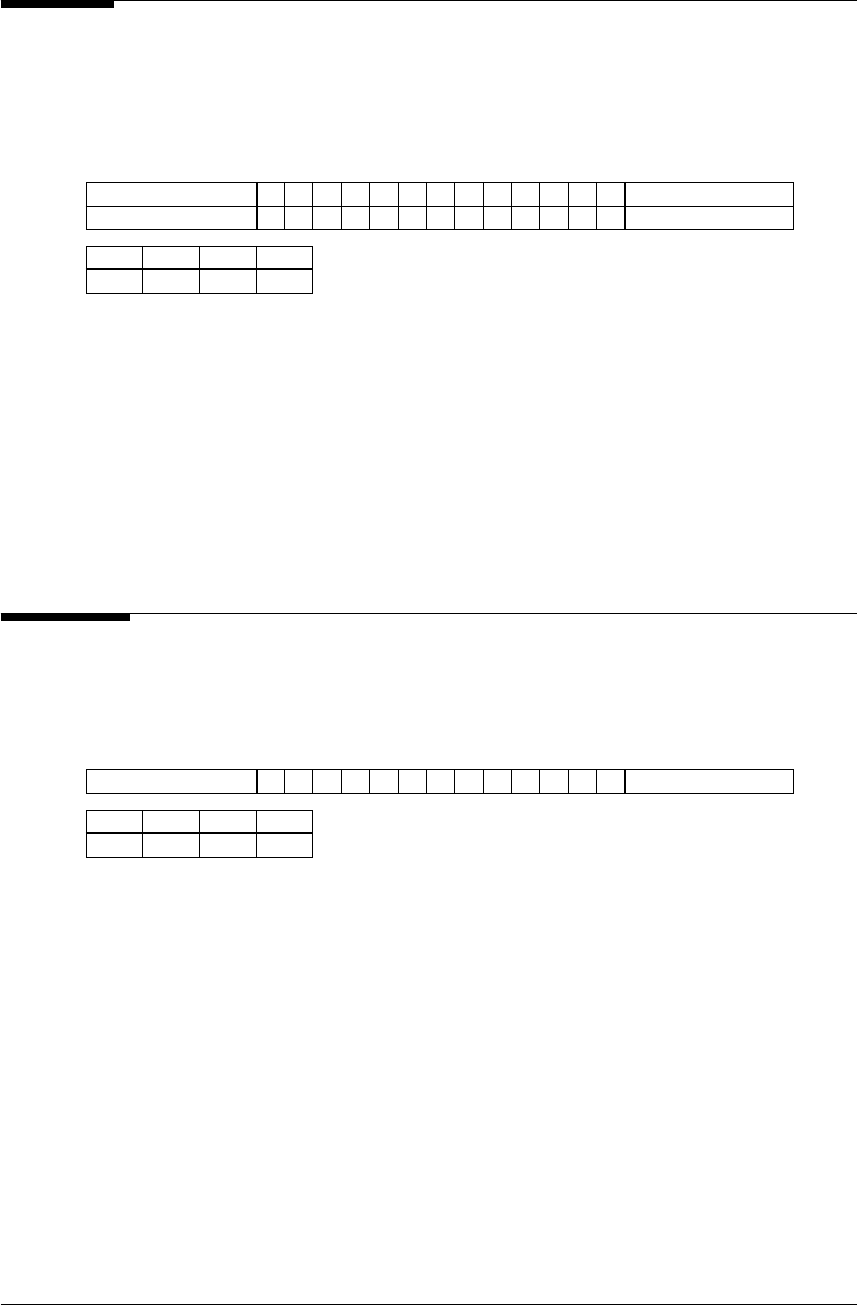

Code: Mnemonic MSB LSB

EX %A,%B 11111111101111FF7H

Flags: EICZ

↓ –––

Mode: Src: Register direct

Dst: Register direct

Extended addressing: Invalid

Decrement stack pointer 1 cycle

Function: sp ← sp - 1

Decrements (-1) the content of the stack pointer sp (SP1 or SP2). This instruction does not

change the C flag regardless of the operation result.

Code:

Mnemonic MSB LSB

DEC %SP1 11111111000001FE0H

DEC %SP2 11111111001001FE4H

Flags: EICZ

↓ ––↕

Mode: Register direct

Extended addressing: Invalid