140 EPSON S1C63000 CORE CPU MANUAL

CHAPTER 4: INSTRUCTION SET

XOR %r,imm4 Exclusive OR immediate data imm4 and r reg. 1 cycle

Function: r ← r ∀ imm4

Performs an exclusive OR operation of the 4-bit immediate data imm4 and the content of the r

register (A or B), and stores the result in the r register.

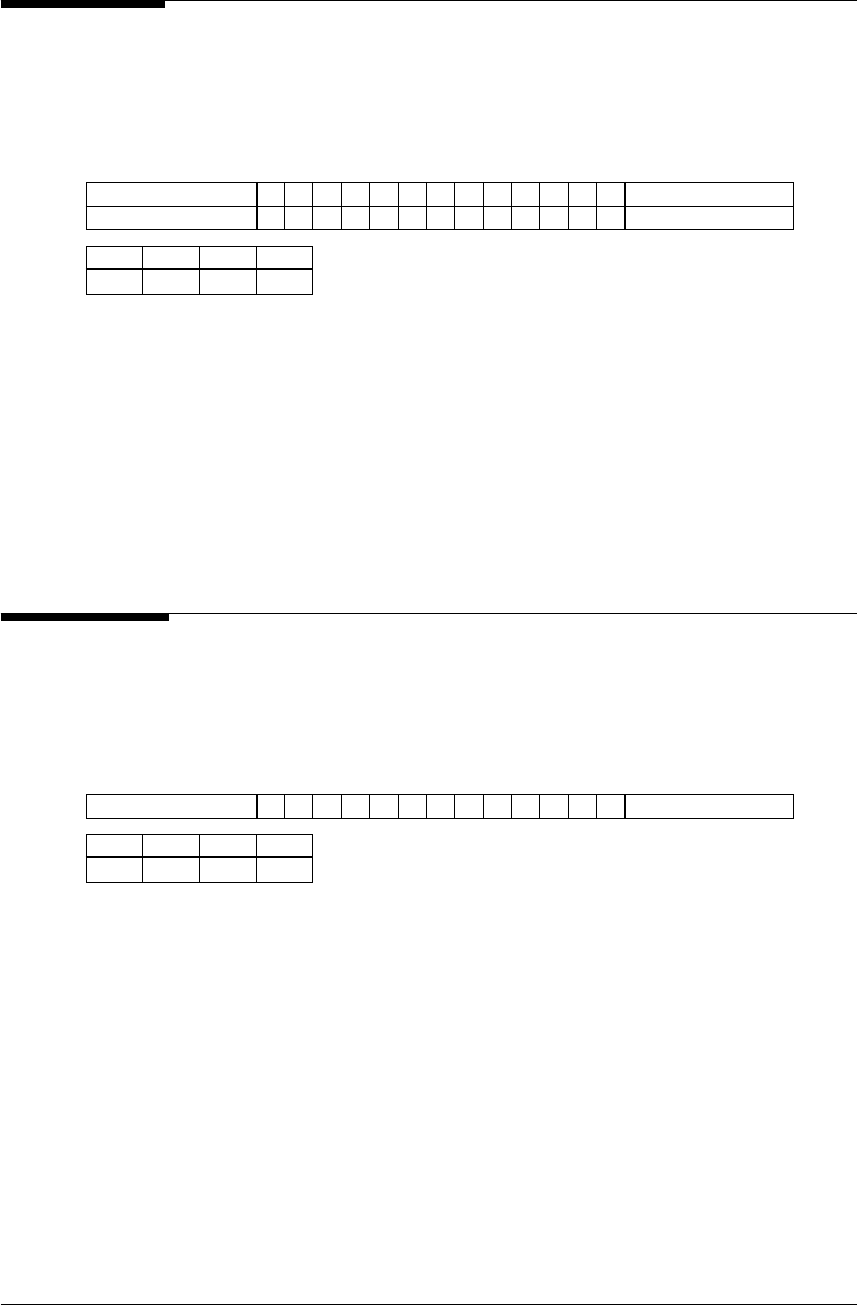

Code:

Mnemonic MSB LSB

XOR %A,imm4 110111100i3i2i1i01BC0H–1BCFH

XOR %B,imm4 110111101i3i2i1i01BD0H–1BDFH

Flags: EICZ

↓ ––↕

Mode: Src: Immediate data

Dst: Register direct

Extended addressing: Invalid

XOR %F,imm4 Exclusive OR immediate data imm4 and F reg. 1 cycle

Function: F ← F ∀ imm4

Performs an exclusive OR operation of the 4-bit immediate data imm4 and the content of the F

(flag) register, and stores the result in the r register. It is possible to set/reset any flag.

Code:

Mnemonic MSB LSB

XOR %F,imm4 100001010i3i2i1i010A0H–10AFH

Flags: EICZ

↕↕↕↕

Mode: Src: Immediate data

Dst: Register direct

Extended addressing: Invalid