S1C63000 CORE CPU MANUAL EPSON 3

CHAPTER 1: OUTLINE

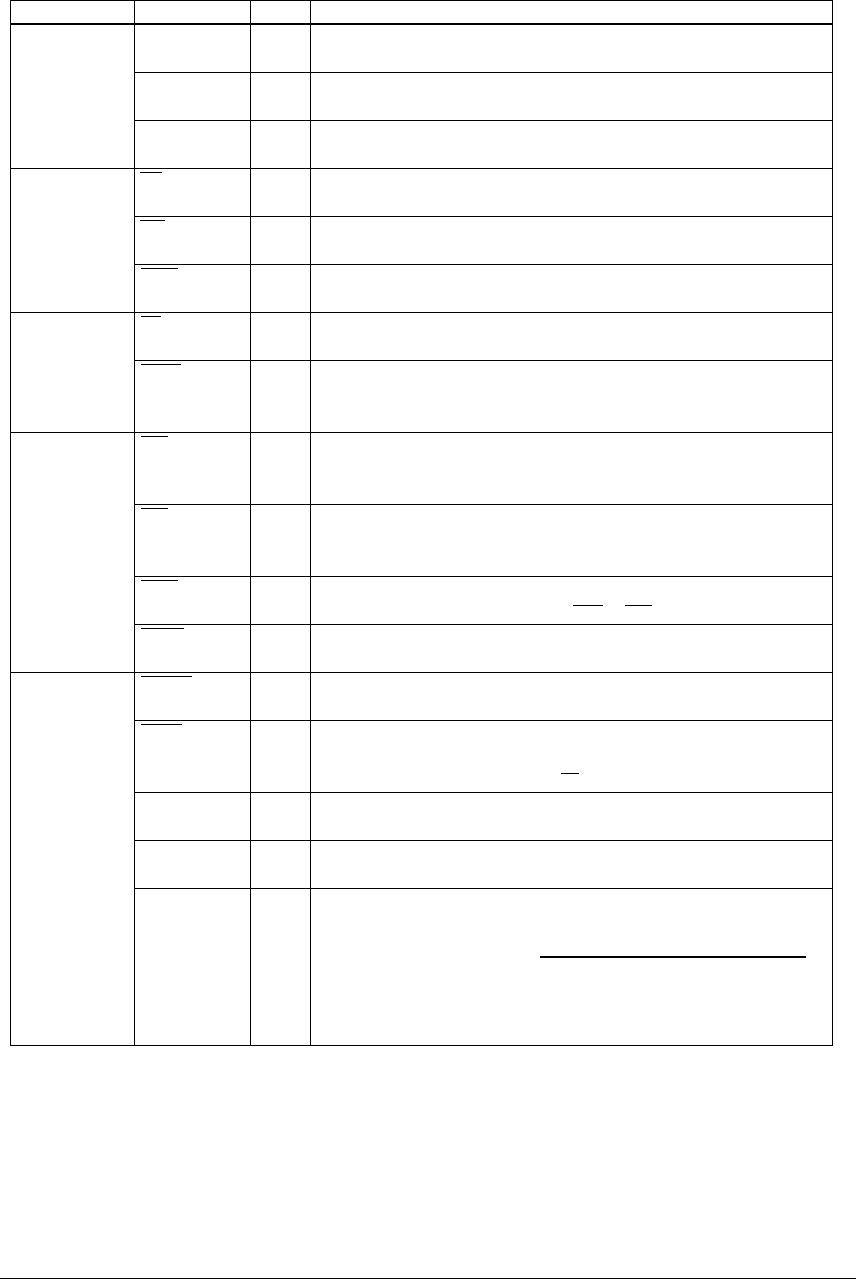

Table 1.4.1(b) Input/output signal list (2)

Type I/O

I

I/O

I/O

O

O

O

I

O

I

I

O

O

O

O

O

O

O

FunctionTerminal name

Data bus

Bus control

signal

System control

signal

Interrupt signal

Status signal

I00–I12

M00–M15

D0–D3

RD

WR

RDIV

SR

USLP

NMI

IRQ

IACK

NACK

FETCH

STOP

IF

BS16

DBS0

DBS1

Instruction bus

Inputs an instruction code.

16-bit data bus

A bidirectional data bus to connect to the RAM (stack RAM) for 16-bit accessing.

4-bit data bus

A bidirectional data bus to connect to the RAM and I/O.

Data read

Goes to a low level when the CPU reads data (from RAM, I/O).

Data write

Goes to a low level when the CPU writes data (to RAM, I/O).

Read interrupt vector

Goes to a low level when the CPU reads an interrupt vector.

Reset input

A low level input resets the CPU.

Micro sleep

Goes to a low level when the CPU executes the SLP instruction.

The peripheral circuit stops oscillation on the basis of this signal.

Non-maskable interrupt request

An interrupt request terminal for an interrupt that cannot be masked by software.

It is accepted at the falling edge of an input signal to this terminal.

Interrupt request

An interrupt request terminal for interrupts that can be masked by software.

It is accepted by a low level signal input to this terminal.

Interrupt acknowledge

Goes to a low level while executing an NMI or IRQ interrupt response cycle.

Non-maskable interrupt acknowledge

Goes to a low level while executing a non-maskable interrupt response cycle.

Fetch cycle

Goes to a low level when the CPU fetches an instruction.

Stop signal

Goes to a low level when the CPU is in stop status after executing the HALT

or SLP instruction, or in reset status (SR is low).

Interrupt flag

Outputs a status (inverted value) of the interrupt flag in the flag (F) register.

16-bit access

Goes to a low level when the CPU accesses to a 16-bit RAM.

Data bus status

Outputs data bus status (for both the 4-bit and 16-bit data bus).

DBS1

0

0

1

1

DBS0

0

1

0

1

State

High impedance

Interrupt vector read

Memory write

Memory read

See Chapter 3, "CPU OPERATION", for the timing of the signals.