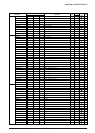

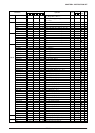

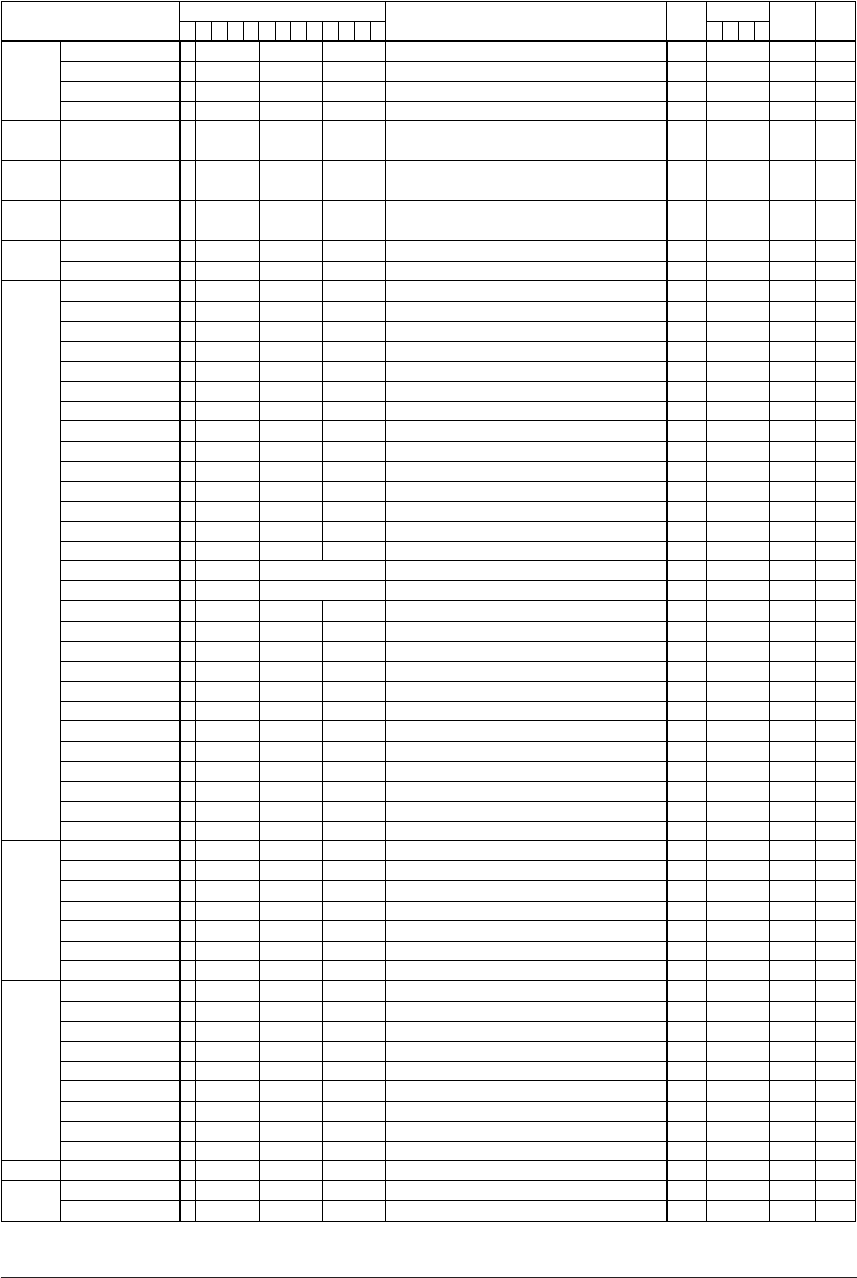

50 EPSON S1C63000 CORE CPU MANUAL

CHAPTER 4: INSTRUCTION SET

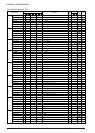

BIT [%Y],imm4

[%Y]+,%A

[%Y]+,%B

[%Y]+,imm4

CALR [00addr6]

CALR sign8

CALZ imm8

CLR [00addr6],imm2

[FFaddr6],imm2

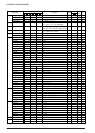

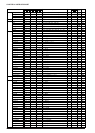

CMP %A,%A

%A,%B

%A,imm4

%A,[%X]

%A,[%X]+

%A,[%Y]

%A,[%Y]+

%B,%A

%B,%B

%B,imm4

%B,[%X]

%B,[%X]+

%B,[%Y]

%B,[%Y]+

%X,imm8

%Y,imm8

[%X],%A

[%X],%B

[%X],imm4

[%X]+,%A

[%X]+,%B

[%X]+,imm4

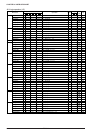

[%Y],%A

[%Y],%B

[%Y],imm4

[%Y]+,%A

[%Y]+,%B

[%Y]+,imm4

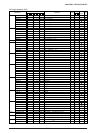

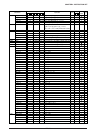

DEC %SP1

%SP2

[%X],n4

[%X]+,n4

[%Y],n4

[%Y]+,n4

[00addr6]

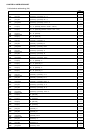

EX %A,%B

%A,[%X]

%A,[%X]+

%A,[%Y]

%A,[%Y]+

%B,[%X]

%B,[%X]+

%B,[%Y]

%B,[%Y]+

HALT

INC %SP1

%SP2

110101010i3i2i1i0

1101011101011

1101011101111

110101011i3i2i1i0

1111100

a5a4a3a2a1a0

00010

s7 s6s5 s4s3 s2s1 s0

00011i7i6i5i4i3i2i1i0

10100i1i0

a5a4a3a2a1a0

10101i1i0

a5a4a3a2a1a0

111100111X000

111100111X010

111100100i3i2i1i0

1111001100000

1111001100001

1111001100010

1111001100011

111100111X100

111100111X110

111100101i3i2i1i0

1111001100100

1111001100101

1111001100110

1111001100111

01110[ FFH - imm8 ]

01111[ FFH - imm8 ]

1111001101000

1111001101100

111100000i3i2i1i0

1111001101001

1111001101101

111100001i3i2i1i0

1111001101010

1111001101110

111100010i3i2i1i0

1111001101011

1111001101111

111100011i3i2i1i0

1111111100000

1111111100100

111001000

n3n2n1n0

111001001

n3n2n1n0

111001010

n3n2n1n0

111001011

n3n2n1n0

1000000

a5a4a3a2a1a0

1111111110111

1000011111000

1000011111001

1000011111010

1000011111011

1000011111100

1000011111101

1000011111110

1000011111111

1111111111100

1111111101000

1111111101100

1 ↓ –– ●

1 ↓ –– ×

1 ↓ –– ×

1 ↓ –– ×

2 ↓ ––– ×

1 ↓ ––– ●

1 ↓ ––– ×

2 ↓ –– ×

2 ↓ –– ×

1 ↓ – ↓↑ ×

1 ↓ – ×

1 ↓ – ×

1 ↓ – ●

1 ↓ – ×

1 ↓ – ●

1 ↓ – ×

1 ↓ – ×

1 ↓ – ↓↑ ×

1 ↓ – ×

1 ↓ – ●

1 ↓ – ×

1 ↓ – ●

1 ↓ – ×

1 ↓ – ●

1 ↓ – ●

1 ↓ – ●

1 ↓ – ●

1 ↓ – ●

1 ↓ – ×

1 ↓ – ×

1 ↓ – ×

1 ↓ – ●

1 ↓ – ●

1 ↓ – ●

1 ↓ – ×

1 ↓ – ×

1 ↓ – ×

1 ↓ –– ×

1 ↓ –– ×

2 ↓ – ●

2 ↓ – ×

2 ↓ – ●

2 ↓ – ×

2 ↓ – ×

1 ↓ ––– ×

2 ↓ ––– ●

2 ↓ ––– ×

2 ↓ ––– ●

2 ↓ ––– ×

2 ↓ ––– ●

2 ↓ ––– ×

2 ↓ ––– ●

2 ↓ ––– ×

2 ↓ ––– ×

1 ↓ –– ×

1 ↓ –– ×

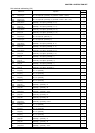

↔↔

[Y]

∧

imm4

[Y]

∧

A, Y ← Y+1

[Y]

∧

B, Y ← Y+1

[Y]

∧

imm4, Y ← Y+1

([(SP1-1)∗4+3]~[(SP1-1)∗4]) ← PC+1,

SP1 ← SP1-1, PC ← PC+[00addr6]+1

([(SP1-1)∗4+3]~[(SP1-1)∗4]) ← PC+1,

SP1 ← SP1-1, PC ← PC+sign8+1 (sign8=-128~127)

([(SP1-1)∗4+3]~[(SP1-1)∗4]) ← PC+1,

SP1 ← SP1-1, PC ← imm8

[00addr6] ← [00addr6]

∧

not (2

imm2

)

[FFaddr6] ← [FFaddr6]

∧

not (2

imm2

)

A-A

A-B

A-imm4

A-[X]

A-[X], X ← X+1

A-[Y]

A-[Y], Y ← Y+1

B-A

B-B

B-imm4

B-[X]

B-[X], X ← X+1

B-[Y]

B-[Y], Y ← Y+1

X-imm8 (imm8=0~255)

Y-imm8 (imm8=0~255)

[X]-A

[X]-B

[X]-imm4

[X]-A, X ← X+1

[X]-B, X ← X+1

[X]-imm4, X ← X+1

[Y]-A

[Y]-B

[Y]-imm4

[Y]-A, Y ← Y+1

[Y]-B, Y ← Y+1

[Y]-imm4, Y ← Y+1

SP1 ← SP1-1

SP2 ← SP2-1

[X] ← N's adjust ([X]-1)

[X] ← N's adjust ([X]-1), X ← X+1

[Y] ← N's adjust ([Y]-1)

[Y] ← N's adjust ([Y]-1), Y ← Y+1

[00addr6] ← [00addr6]-1

A ↔ B

A ↔ [X]

A ↔ [X], X ← X+1

A ↔ [Y]

A ↔ [Y], Y ← Y+1

B ↔ [X]

B ↔ [X], X ← X+1

B ↔ [Y]

B ↔ [Y], Y ← Y+1

Halt

SP1 ← SP1+1

SP2 ← SP2+1

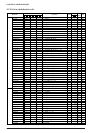

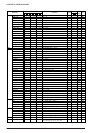

Mnemonic

Machine code

Operation Cycle Page

Flag EXT.

mode

12

EICZ

11109876543210

↔↔↔↔↔↔

↔

↔↔↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

81

80

80

81

82

82

83

83

83

84

84

84

85

85

85

85

84

84

84

85

85

85

85

88

88

86

86

87

86

86

87

86

86

87

86

86

87

90

90

89

89

89

89

88

90

91

91

91

91

91

91

91

91

92

94

94