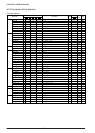

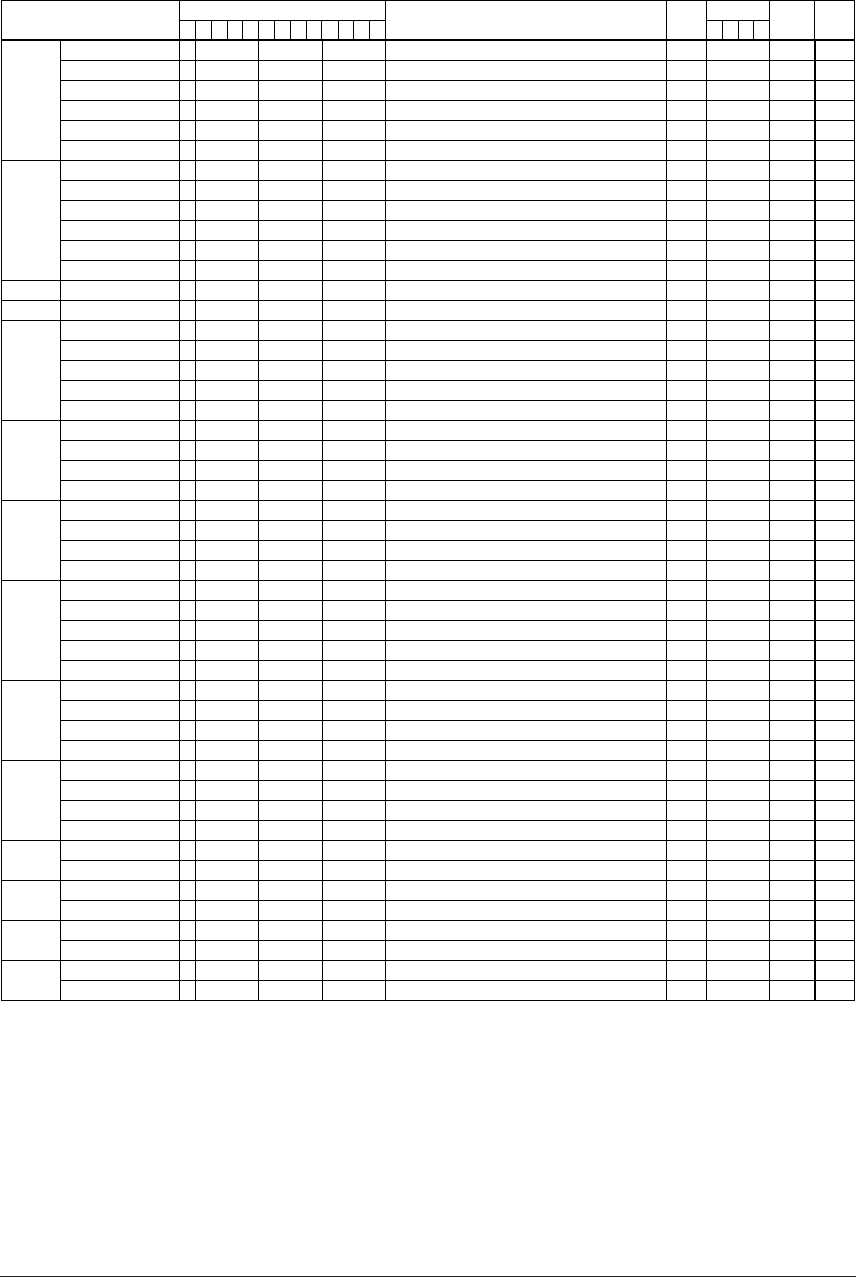

S1C63000 CORE CPU MANUAL EPSON 43

CHAPTER 4: INSTRUCTION SET

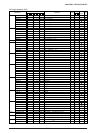

CMP [%X],%A

[%X],%B

[%X],imm4

[%X]+,%A

[%X]+,%B

[%X]+,imm4

CMP [%Y],%A

[%Y],%B

[%Y],imm4

[%Y]+,%A

[%Y]+,%B

[%Y]+,imm4

INC [00addr6]

DEC [00addr6]

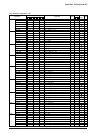

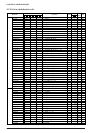

ADC %B,%A,n4

∗1 %B,[%X],n4

%B,[%X]+,n4

%B,[%Y],n4

%B,[%Y]+,n4

ADC [%X],%B,n4

∗1 [%X],0,n4

[%X]+,%B,n4

[%X]+,0,n4

ADC [%Y],%B,n4

∗1 [%Y],0,n4

[%Y]+,%B,n4

[%Y]+,0,n4

SBC %B,%A,n4

∗1 %B,[%X],n4

%B,[%X]+,n4

%B,[%Y],n4

%B,[%Y]+,n4

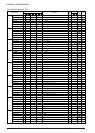

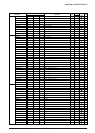

SBC [%X],%B,n4

∗1 [%X],0,n4

[%X]+,%B,n4

[%X]+,0,n4

SBC [%Y],%B,n4

∗1 [%Y],0,n4

[%Y]+,%B,n4

[%Y]+,0,n4

INC [%X],n4

∗1 [%X]+,n4

INC [%Y],n4

∗1 [%Y]+,n4

DEC [%X],n4

∗1 [%X]+,n4

DEC [%Y],n4

∗1 [%Y]+,n4

1111001101000

1111001101100

111100000i3i2i1i0

1111001101001

1111001101101

111100001i3i2i1i0

1111001101010

1111001101110

111100010i3i2i1i0

1111001101011

1111001101111

111100011i3i2i1i0

1000001

a5a4a3a2a1a0

1000000

a5a4a3a2a1a0

100001101

[ 10H-n4 ]

111011100

[ 10H-n4 ]

111011101

[ 10H-n4 ]

111011110

[ 10H-n4 ]

111011111

[ 10H-n4 ]

111010100

[ 10H-n4 ]

111010000

[ 10H-n4 ]

111010101

[ 10H-n4 ]

111010001

[ 10H-n4 ]

111010110

[ 10H-n4 ]

111010010

[ 10H-n4 ]

111010111

[ 10H-n4 ]

111010011

[ 10H-n4 ]

100001100

n3n2n1n0

111001100

n3n2n1n0

111001101

n3n2n1n0

111001110

n3n2n1n0

111001111

n3n2n1n0

111000100

n3n2n1n0

111000000

n3n2n1n0

111000101

n3n2n1n0

111000001

n3n2n1n0

111000110

n3n2n1n0

111000010

n3n2n1n0

111000111

n3n2n1n0

111000011

n3n2n1n0

111011000

[ 10H-n4 ]

111011001

[ 10H-n4 ]

111011010

[ 10H-n4 ]

111011011

[ 10H-n4 ]

111001000

n3n2n1n0

111001001

n3n2n1n0

111001010

n3n2n1n0

111001011

n3n2n1n0

1 ↓ – ●

1 ↓ – ●

1 ↓ – ●

1 ↓ – ×

1 ↓ – ×

1 ↓ – ×

1 ↓ – ●

1 ↓ – ●

1 ↓ – ●

1 ↓ – ×

1 ↓ – ×

1 ↓ – ×

2 ↓ – ×

2 ↓ – ×

2 ↓ – ×

2 ↓ – ●

2 ↓ – ×

2 ↓ – ●

2 ↓ – ×

2 ↓ – ●

2 ↓ – ●

2 ↓ – ×

2 ↓ – ×

2 ↓ – ●

2 ↓ – ●

2 ↓ – ×

2 ↓ – ×

2 ↓ – ×

2 ↓ – ●

2 ↓ – ×

2 ↓ – ●

2 ↓ – ×

2 ↓ – ●

2 ↓ – ●

2 ↓ – ×

2 ↓ – ×

2 ↓ – ●

2 ↓ – ●

2 ↓ – ×

2 ↓ – ×

2 ↓ – ●

2 ↓ – ×

2 ↓ – ●

2 ↓ – ×

2 ↓ – ●

2 ↓ – ×

2 ↓ – ●

2 ↓ – ×

[X]-A

[X]-B

[X]-imm4

[X]-A, X ← X+1

[X]-B, X ← X+1

[X]-imm4, X ← X+1

[Y]-A

[Y]-B

[Y]-imm4

[Y]-A, Y ← Y+1

[Y]-B, Y ← Y+1

[Y]-imm4, Y ← Y+1

[00addr6] ← [00addr6]+1

[00addr6] ← [00addr6]-1

B ← N's adjust (B+A+C)

B ← N's adjust (B+[X]+C)

B ← N's adjust (B+[X]+C), X ← X+1

B ← N's adjust (B+[Y]+C)

B ← N's adjust (B+[Y]+C), Y ← Y+1

[X] ← N's adjust ([X]+B+C)

[X] ← N's adjust ([X]+0+C)

[X] ← N's adjust ([X]+B+C), X ← X+1

[X] ← N's adjust ([X]+0+C), X ← X+1

[Y] ← N's adjust ([Y]+B+C)

[Y] ← N's adjust ([Y]+0+C)

[Y] ← N's adjust ([Y]+B+C), Y ← Y+1

[Y] ← N's adjust ([Y]+0+C), Y ← Y+1

B ← N's adjust (B-A-C)

B ← N's adjust (B-[X]-C)

B ← N's adjust (B-[X]-C), X ← X+1

B ← N's adjust (B-[Y]-C)

B ← N's adjust (B-[Y]-C), Y ← Y+1

[X] ← N's adjust ([X]-B-C)

[X] ← N's adjust ([X]-0-C)

[X] ← N's adjust ([X]-B-C), X ← X+1

[X] ← N's adjust ([X]-0-C), X ← X+1

[Y] ← N's adjust ([Y]-B-C)

[Y] ← N's adjust ([Y]-0-C)

[Y] ← N's adjust ([Y]-B-C), Y ← Y+1

[Y] ← N's adjust ([Y]-0-C), Y ← Y+1

[X] ← N's adjust ([X]+1)

[X] ← N's adjust ([X]+1), X ← X+1

[Y] ← N's adjust ([Y]+1)

[Y] ← N's adjust ([Y]+1), Y ← Y+1

[X] ← N's adjust ([X]-1)

[X] ← N's adjust ([X]-1), X ← X+1

[Y] ← N's adjust ([Y]-1)

[Y] ← N's adjust ([Y]-1), Y ← Y+1

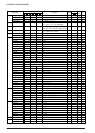

Mnemonic

Machine code

Operation Cycle Page

Flag EXT.

mode

12

EICZ

11109876543210

↔

↔

ALU alithmetic operation (3/3)

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

↔

"n4" should be specified with a value between 1 and 16 that indicates a radix.

In the ADC and INC instructions, the assembler converts the "n4" into a complement, and places it at the low-order 4 bits in

the machine code.

In the SBC and DEC instructions, the "n4" is placed as it is at the low-order 4 bits in the machine code.

(However, when 16 is specified to n4, the machine code is generated with 0000H as the low-order 4 bits.)

∗1

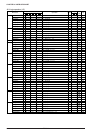

86

86

87

86

86

87

86

86

87

86

86

87

92

88

65

65

66

65

66

66

67

67

68

66

67

67

68

127

128

128

128

128

129

130

129

130

129

130

129

130

93

93

93

93

89

89

89

89