Chapter 5 Operation 61

to the output amplifier where the electrons are grouped as electrons/count. This result

leaves the CCD and goes to the preamplifier where gain is applied.

WinView and WinSpec allow you to specify the type of readout, binning, the output

am

plifier, and the gain (the number of electrons required to generate an ADU).

Note: The type of readout (full frame, frame transfer, or interline) depends on the CCD

array installed in the camera.

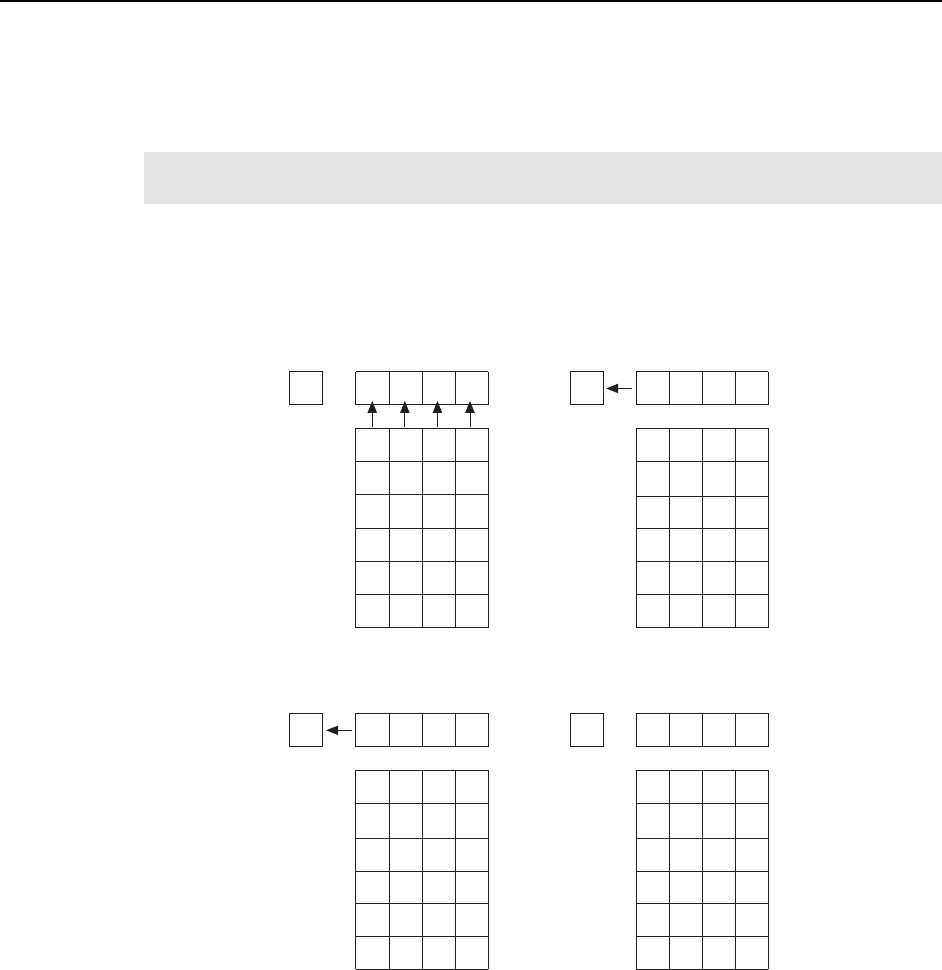

The upper left drawing in Figure 21 represents a CCD after exposure but before the

beginning of readout. The capital letters repr

esent different amounts of charge, including

both signal and dark charge. This section explains readout at full resolution, where every

pixel is digitized separately.

Empty Readout Register Readout Register with charge

from first line.

Charge from first cell shifted

into Output Node.

After first line is read out,next line

can be shifted into empty

Readout Register.

A2

A1

B2

B1

C2

C1

D2

D1

A4

A3

B4

B3

C4

C3

D4

D3

A6

A5

B6

B5

C6

C5

D6

D5

A1 B1 C1 D1

A2 B2 C2 D2

A4

A3

B4

B3

C4

C3

D4

D3

A6 B6

C6

D6

A2 B2 C2 D2

A4

A3

B4

B3

C4

C3

D4

D3

A6 B6

C6

D6

A2

A1

B2

B1

C2

C1

D2

D1

A4

A3

B4

B3

C4

C3

D4

D3

A6 B6

C6

D6

A5 B5 C5 D5

A5 B5 C5 D5 A5 B5 C5 D5

43

12

Figure 21. Full Frame at Full Resolution

Readout of the CCD begins with the simultaneous shifting of all pixels one row toward

the "shift register", in this case the row at top. The shift register is a single line of pixels

along one edge of the CCD, not sensitive to light and used for readout only. Typically the

shift register pixels hold twice as much charge as the pixels in the imaging area of the

CCD.

After the first row is moved into the shift register, the charge now in the shift register is

shifted toward the output node, located at one end of the shift register. As each value is

"em

ptied" into this node it is digitized. Only after all pixels in the first row are digitized is

the second row moved into the shift register. The order of shifting in our example is

therefore A1, B1, C1, D1, A2, B2, C2, D2, A3....