Clock Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 6-7

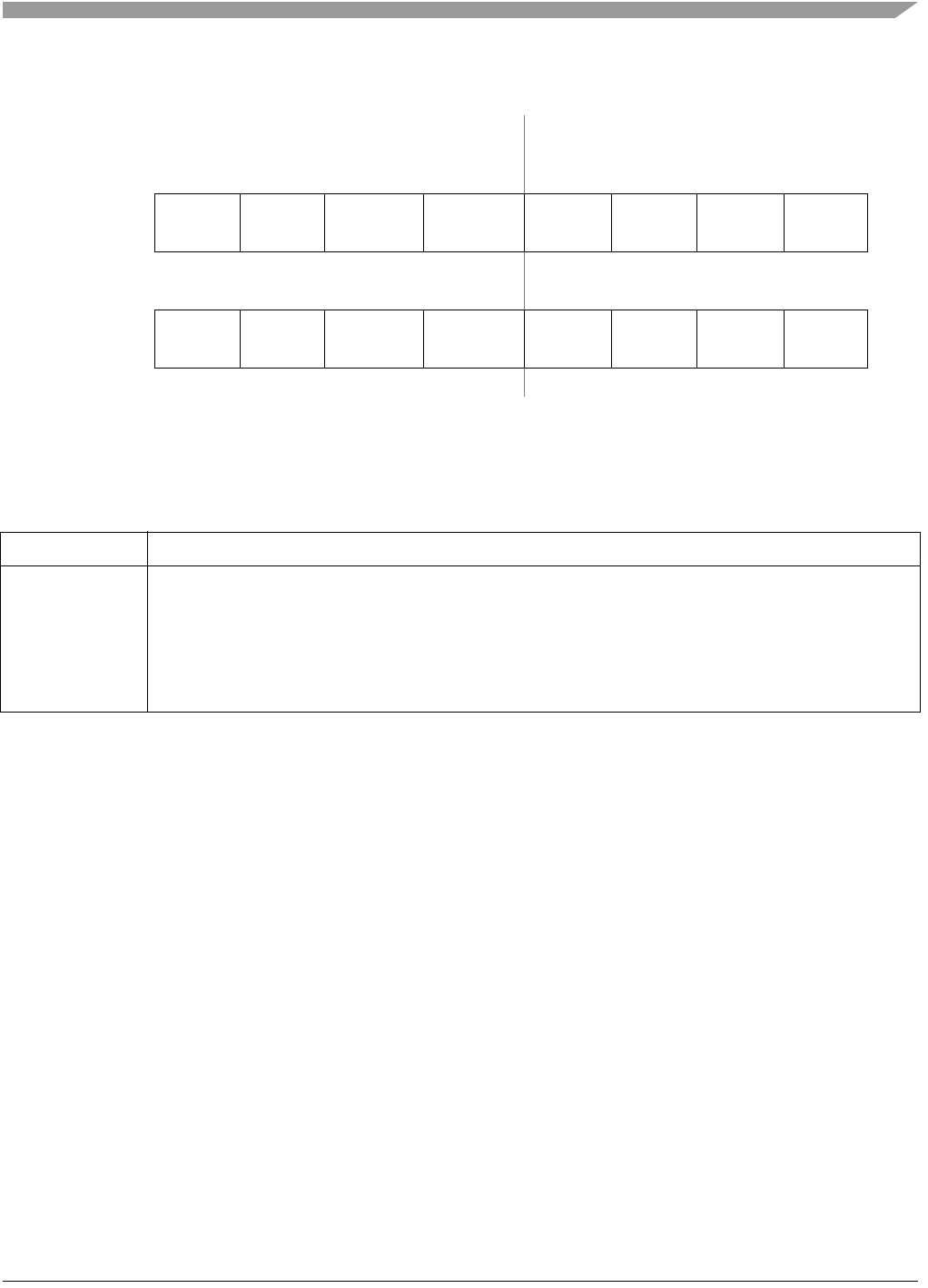

6.7.1.1 Synthesizer Control Register (SYNCR)

IPSBAR

Offset: 0x12_0000 (SYNCR)

Access: Supervisor read/write

15 14 13 12 11 10 9 8

R

LOLRE MFD2 MFD1 MFD0 LOCRE RFD2 RFD1 RFD0

W

Reset 0 0 0 1 0 0 0 0

76 5 4 3210

R

LOCEN DISCLK FWKUP — — CLKSRC

1

1

The reset value of PLLEN and CLKSRC depend on the value of CLKMOD1 during reset (set to 1 if PLL is

enabled when the device emerges from reset).

PLLMODE PLLEN

1

W

Reset 0 0 0 0 0 0 1 0

Figure 6-2. Synthesizer Control Register (SYNCR)

Table 6-5. SYNCR Field Descriptions

Field Description

15

LOLRE

Loss-of-lock reset enable. Determines how the system manages a loss-of-lock indication. When operating

in normal mode or 1:1 PLL mode, the PLL must be locked before setting the LOLRE bit. Otherwise, reset

is immediately asserted. To prevent an immediate reset, the LOLRE bit must be cleared before writing the

MFD[2:0] bits or entering stop mode with the PLL disabled.

0 No reset on loss of lock

1 Reset on loss of lock

Note: In external clock mode, the LOLRE bit has no effect.