ColdFire Core

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

3-22 Freescale Semiconductor

ColdFire processors load hardware configuration information into the D0 and D1 general-purpose

registers after system reset. The hardware configuration information is loaded immediately after the

reset-in signal is negated. This allows an emulator to read out the contents of these registers via the BDM

to determine the hardware configuration.

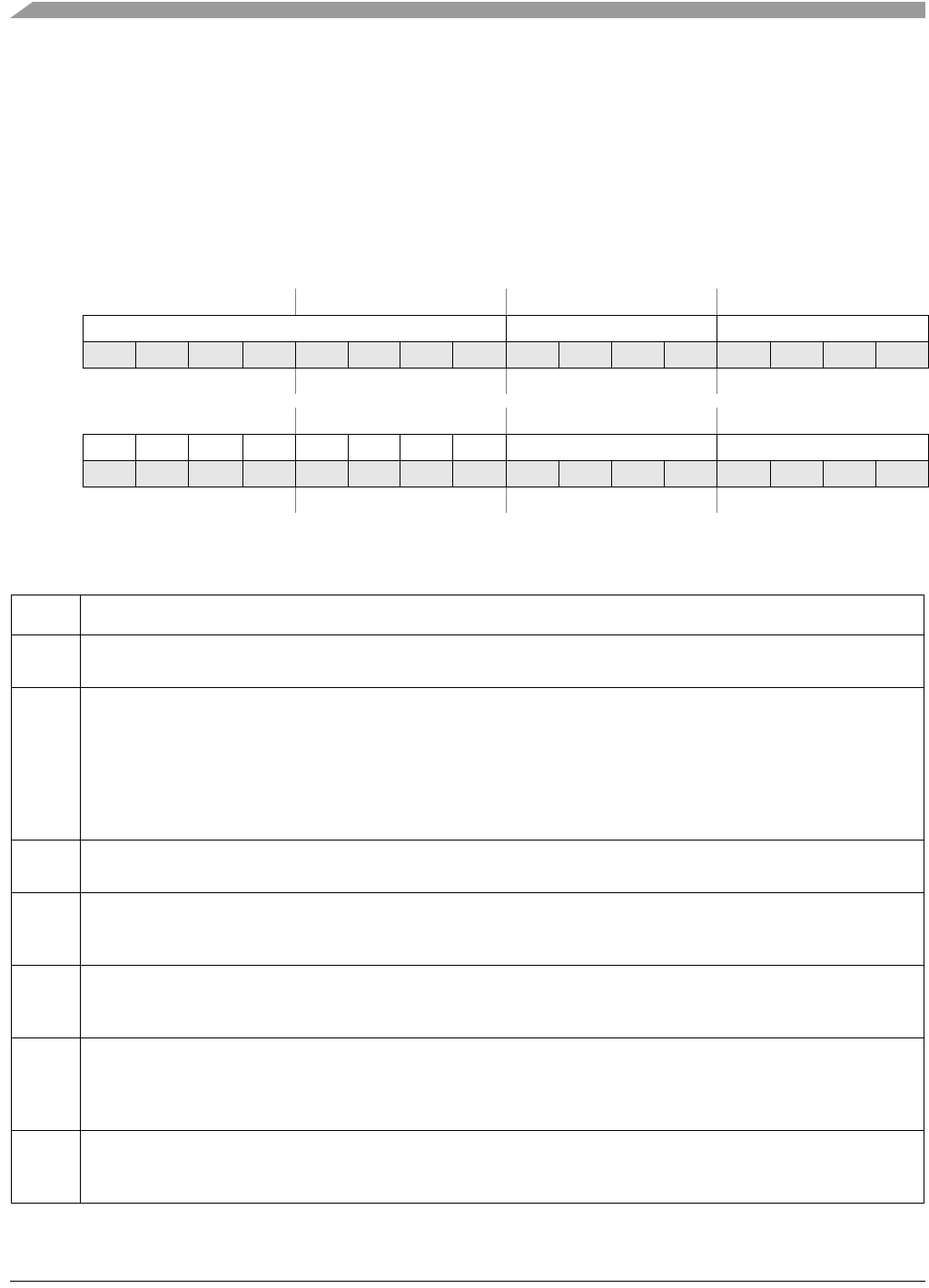

Information loaded into D0 defines the processor hardware configuration as shown in Figure 3-18.

BDM: Load: 0x080 (D0)

Store: 0x180 (D0)

Access: User read-only

BDM read-only

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R PF VER REV

W

Reset110011110010 0000

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R MAC DIVEMACFPUMMU000 ISA DEBUG

W

Reset1100000010001001

Figure 3-18. D0 Hardware Configuration Info

Table 3-9. D0 Hardware Configuration Info Field Description

Field Description

31–24

PF

Processor family. This field is fixed to a hex value of 0xCF indicating a ColdFire core is present.

23–20

VER

ColdFire core version number. Defines the hardware microarchitecture version of ColdFire core.

0001 V1 ColdFire core

0010 V2 ColdFire core (This is the value used for this device.)

0011 V3 ColdFire core

0100 V4 ColdFire core

0101 V5 ColdFire core

Else Reserved for future use.

19–16

REV

Processor revision number. The default is 0b0000.

15

MAC

MAC present. This bit signals if the optional multiply-accumulate (MAC) execution engine is present in processor core.

0 MAC execute engine not present in core.

1 MAC execute engine is present in core. (This is the value used for this device.)

14

DIV

Divide present. This bit signals if the hardware divider (DIV) is present in the processor core.

0 Divide execute engine not present in core.

1 Divide execute engine is present in core. (This is the value used for this device.)

13

EMAC

EMAC present. This bit signals if the optional enhanced multiply-accumulate (EMAC) execution engine is present in

processor core.

0 EMAC execute engine not present in core. (This is the value used for this device.)

1 EMAC execute engine is present in core.

12

FPU

FPU present. This bit signals if the optional floating-point (FPU) execution engine is present in processor core.

0 FPU execute engine not present in core. (This is the value used for this device.)

1 FPU execute engine is present in core.