General Purpose Timer Module (GPT)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 21-11

21.6.11 GPT System Control Register 2 (GPTSCR2)

Table 21-13. GPTIE Field Descriptions

Field Description

7–4 Reserved, should be cleared.

3–0

Cnl

Channel interrupt enable. Enables the C[3:0]F flags in GPT flag register 1 to generate interrupt requests for each

channel. These bits are read anytime, write anytime.

1 Corresponding channel interrupt requests enabled

0 Corresponding channel interrupt requests disabled

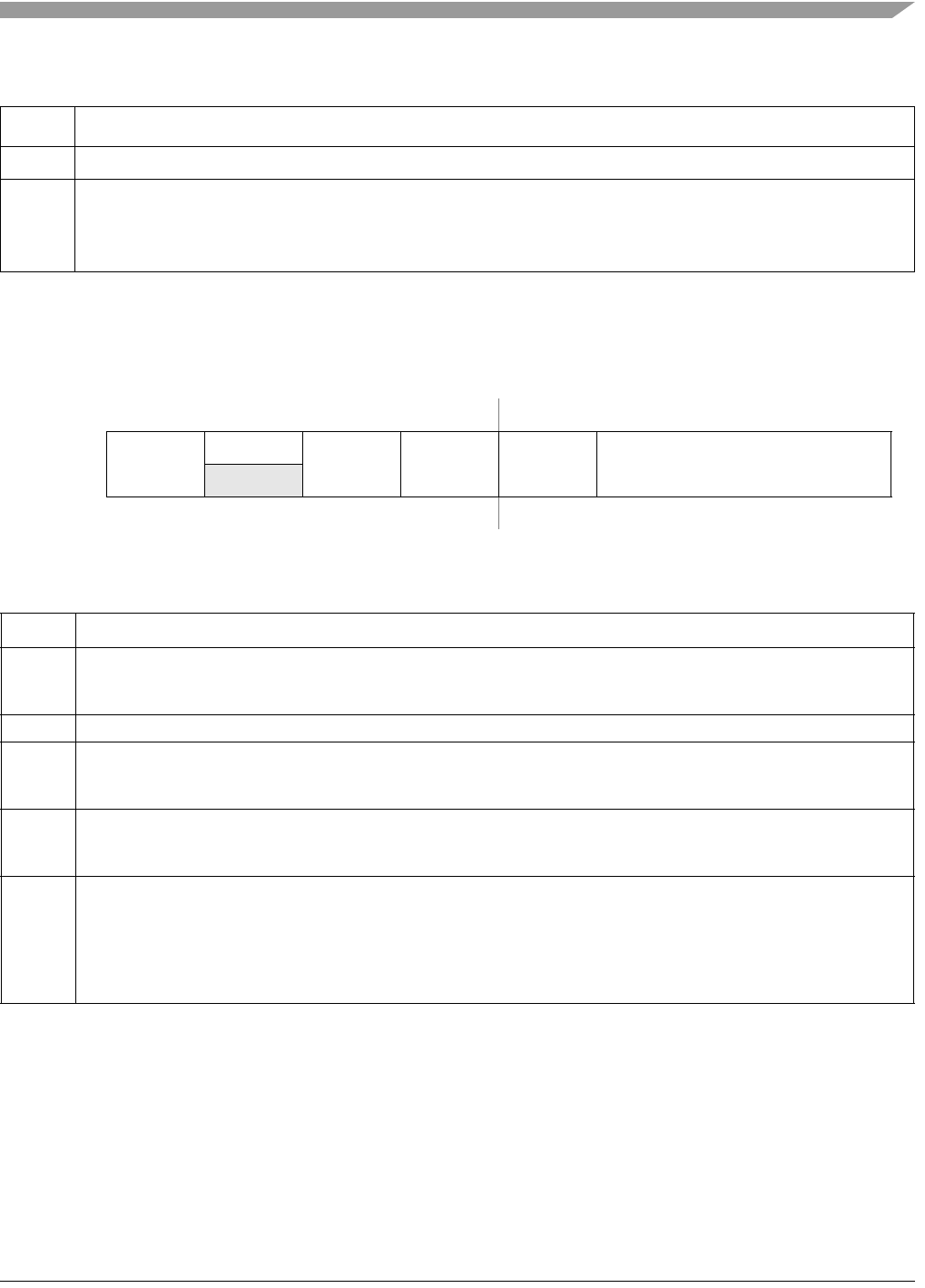

IPSBAR

Offset: 0x1A_000D (GPTSCR2)

Access: Supervisor read/write

76543210

R

TOI

0

PUPT RDPT TCRE PR

W

Reset:00000000

Figure 21-13. GPT System Control Register 2 (GPTSCR2)

Table 21-14. GPTSCR2 Field Descriptions

Field Description

7

TOI

Enables timer overflow interrupt requests.

1 Overflow interrupt requests enabled

0 Overflow interrupt requests disabled

6 Reserved, should be cleared.

5

PUPT

Enables pull-up resistors on the GPT ports when the ports are configured as inputs.

1 Pull-up resistors enabled

0 Pull-up resistors disabled

4

RDPT

GPT drive reduction. Reduces the output driver size.

1 Output drive reduction enabled

0 Output drive reduction disabled

3

TCRE

Enables a counter reset after a channel 3 compare.

1 Counter reset enabled

0 Counter reset disabled

Note: When the GPT channel 3 registers contain 0x0000 and TCRE is set, the GPT counter registers remain at

0x0000 all the time. When the GPT channel 3 registers contain 0xFFFF and TCRE is set, TOF does not get set even

though the GPT counter registers go from 0xFFFF to 0x0000.