DMA Controller Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 17-9

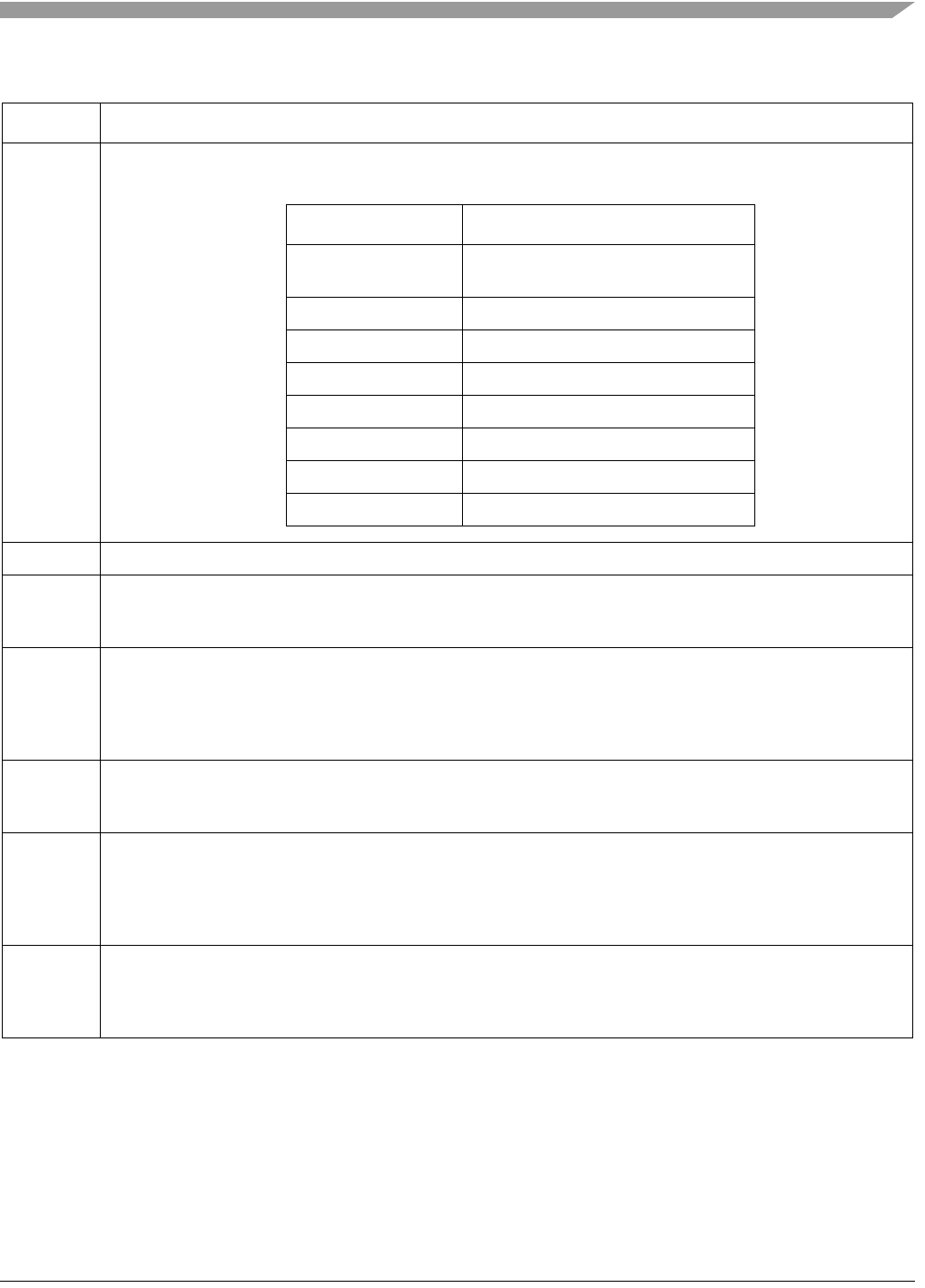

27–25

BWC

Bandwidth control. Indicates the number of bytes in a block transfer. When the byte count reaches a multiple of

the BWC value, the DMA releases the bus.

24-23 Reserved, should be cleared.

22

SINC

Source increment. Controls whether a source address increments after each successful transfer.

0 No change to SAR after a successful transfer.

1 The SAR increments by 1, 2, 4, or 16, as determined by the transfer size.

21–20

SSIZE

Source size. Determines the data size of the source bus cycle for the DMA control module.

00 Longword

01 Byte

10 Word

11 Line (16-byte burst)

19

DINC

Destination increment. Controls whether a destination address increments after each successful transfer.

0 No change to the DAR after a successful transfer.

1 The DAR increments by 1, 2, 4, or 16, depending upon the size of the transfer.

18–17

DSIZE

Destination size. Determines the data size of the destination bus cycle for the DMA controller.

00 Longword

01 Byte

10 Word

11 Line (16-byte burst)

16

START

Start transfer.

0DMA inactive

1 The DMA begins the transfer in accordance to the values in the control registers. START is cleared

automatically after one system clock and is always read as logic 0.

Table 17-4. DCRn Field Descriptions (continued)

Field Description

BWC Number of kilobytes per block

000 DMA has priority and does not negate

its request until transfer completes.

001 16 Kbytes

010 32 Kbytes

011 64 Kbytes

100 128 Kbytes

101 256 Kbytes

110 512 Kbytes

111 1024 Kbytes