Pulse-Width Modulation (PWM) Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 27-11

27.2.11 PWM Channel Duty Registers (PWMDTYn)

The PWM duty registers determine the duty cycle of the associated PWM channel. To calculate the output

duty cycle (high time as a percentage of period) for a particular channel:

Eqn. 27-4

For boundary case programming values (e.g. PWMDTYn = 0x00 or PWMDTYn >PWMPERn), refer to

Section Section 27.3.2.8, “PWM Boundary Cases”.

IPSBAR

Offset:

0x1B_0014 (PWMPER0)

0x1B_0015 (PWMPER1)

0x1B_0016 (PWMPER2)

0x1B_0017 (PWMPER3)

0x1B_0018 (PWMPER4)

0x1B_0019 (PWMPER5)

0x1B_001A (PWMPER6)

0x1B_001B (PWMPER7)

Access: User Read/Write

76543210

R

PERIOD

W

Reset:11111111

Figure 27-11. PWM Period Registers (PWMPERn)

Table 27-11. PWMPERn Field Descriptions

Field Description

7–0

PERIOD

Period counter for the output PWM signal.

If PERIOD equals 0x00, the PWMn output is always high (PPOLn=1) or always low (PPOLn=0). See

Section 27.3.2.8, “PWM Boundary Cases” for other special cases.

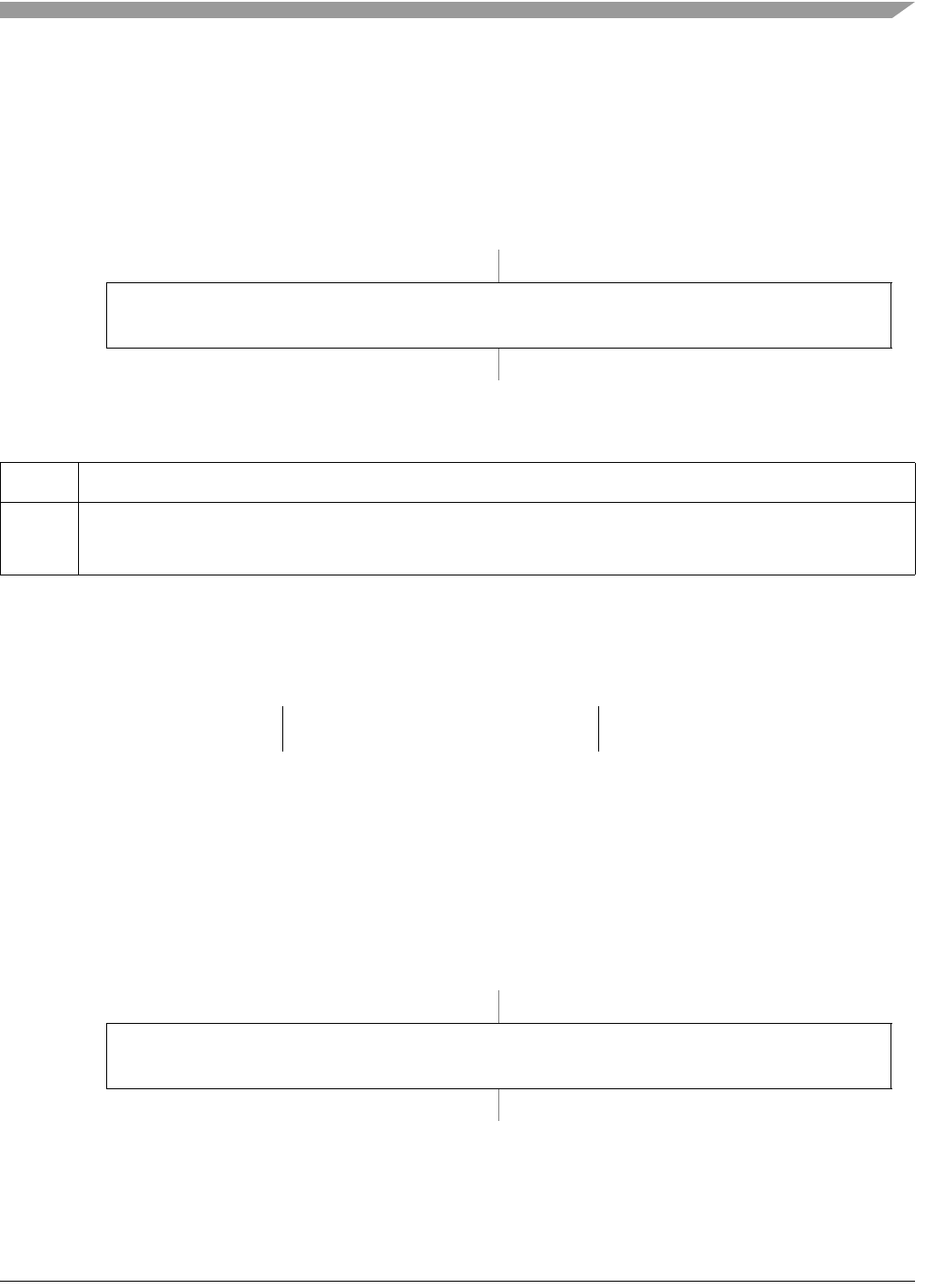

IPSBAR

Offset:

0x1B_001C (PWMDTY0)

0x1B_001D (PWMDTY1)

0x1B_001E (PWMDTY2)

0x1B_001F (PWMDTY3)

0x1B_0020 (PWMDTY4)

0x1B_0021 (PWMDTY5)

0x1B_0022 (PWMDTY6)

0x1B_0023 (PWMDTY7)

Access: User Read/Write

76543210

R

DUTY

W

Reset:11111111

Figure 27-12. PWM Duty Registers (PWMDTYn)

Duty Cycle 1 PWMPOL PPOLn[]

PWMDTYn

PWMPERn

------------------------------

––

⎝⎠

⎛⎞

100%×=