Clock Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 6-13

6.7.1.7 Oscillator Control High Register (OCHR)

The OCHR is used to enable and configure the relaxation oscillator.

IPSBAR

Offset: 0x12_0009 (CCLR)

Access: Supervisor read/write

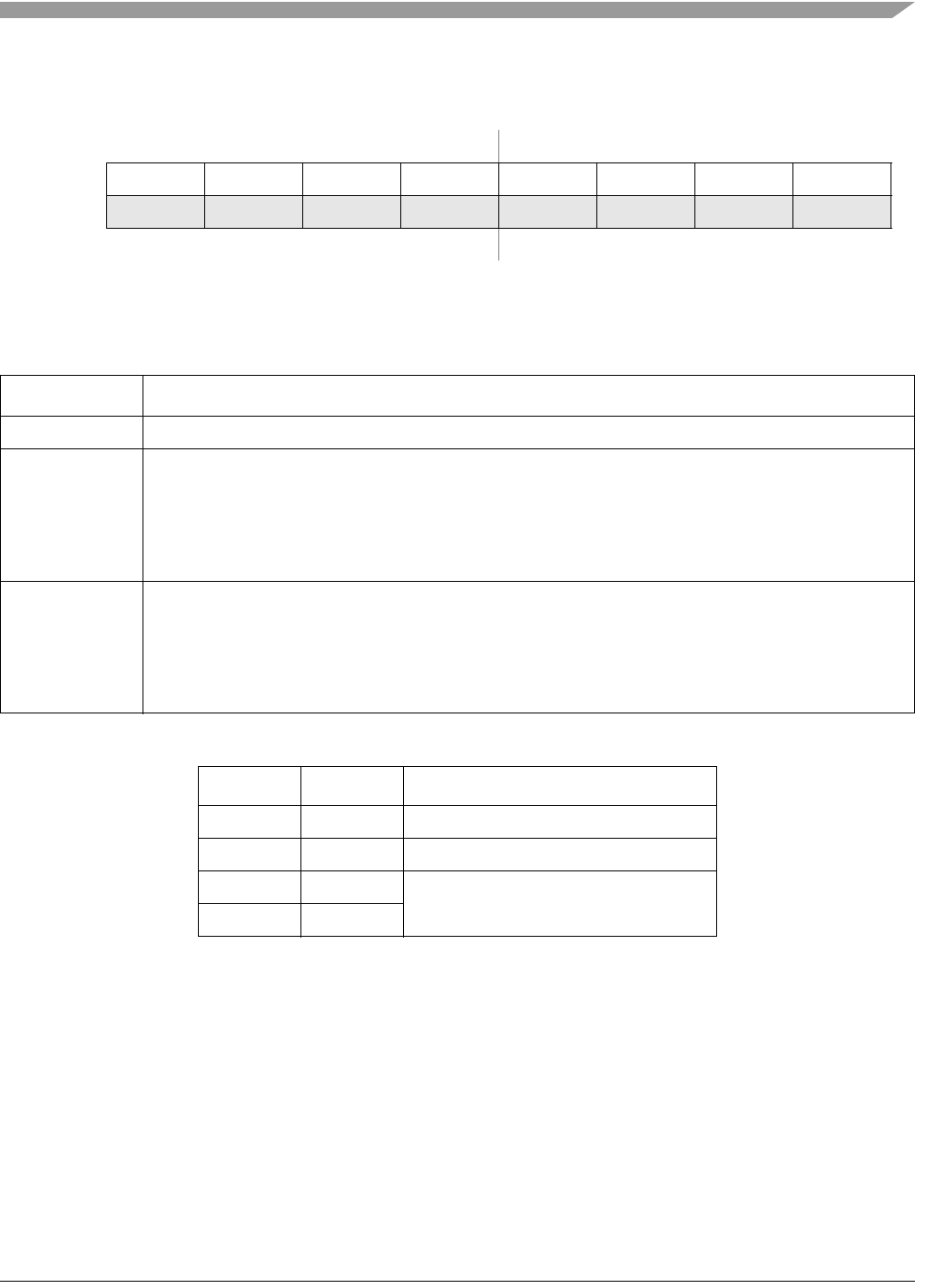

76543210

R — — — — — — OSCSEL1 OSCSEL0

W

Reset:0000000See note

1

1

The OSCSEL reset state is determined during reset configuration.

Figure 6-7. Clock Control Low Register (CCLR)

Table 6-10. CCLR Field Descriptions

Field Description

7–1 Reserved, should be cleared.

1

OSCSEL1

Oscillator Select 1 bit. This bit works in conjunction with the OSCSEL0 bit to select the clock source for the

PLL input/bypass clock, as shown in Tabl e 6-11 .

0 PLL input/bypass clock comes from the external oscillator.

1 PLL input/bypass clock comes from the relaxation oscillator.

Note: When switching clock sources, the module ensures that, during the changeover, no spurious glitches

occur in the system clock, and that the crystal and relaxation oscillators remain enabled.

0

OSCSEL0

Oscillator Select 0 bit. This bit works in conjunction with the OSCSEL1 bit to select the clock source for the

PLL input/bypass clock, as shown in Tabl e 6-11 .

0 PLL input/bypass clock comes from the primary oscillator.

1 PLL input/bypass clock comes from the relaxation oscillator.

Note: When switching clock sources, the module ensures that, during the changeover, no spurious glitches

occur in the system clock, and that the crystal and relaxation oscillators remain enabled.

Table 6-11. CCLR[OSCSEL1] and CCLR[OSCSEL0] Settings

OSCSEL1 OSCSEL0 Source of PLL input/bypass clock

0 0 Primary oscillator (default)

0 1 Relaxation oscillator

10

Secondary oscillator

11