System Control Module (SCM)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

12-14 Freescale Semiconductor

12.7.3.1 Master Privilege Register (MPR)

The MPR specifies the access privilege level associated with each bus master in the platform. The register

provides one bit per bus master. Bit 3 is reserved and should be cleared. Bits 2:0 correspond to master 2

(DMA Controller), master 1 (internal bus master), and master 0 (ColdFire core), respectively.

Only trusted bus masters can modify the access control registers. If a non-trusted bus master attempts to

write any of the SACU control registers, the access is aborted with an error termination and the registers

remain unaffected.

The processor core is connected to bus master 0 and is always treated as a trusted bus master. Accordingly,

MPR[0] is forced to 1 at reset.

12.7.3.2 Peripheral Access Control Registers (PACR0–PACR8)

Access to several on-chip peripherals is controlled by shared peripheral access control registers. A single

PACR defines the access level for each of the two modules. These modules only support operand reads

and writes. Each PACR follows the format illustrated in Figure 12-9. For a list of PACRs and the modules

that they control, refer to Table 12-12.

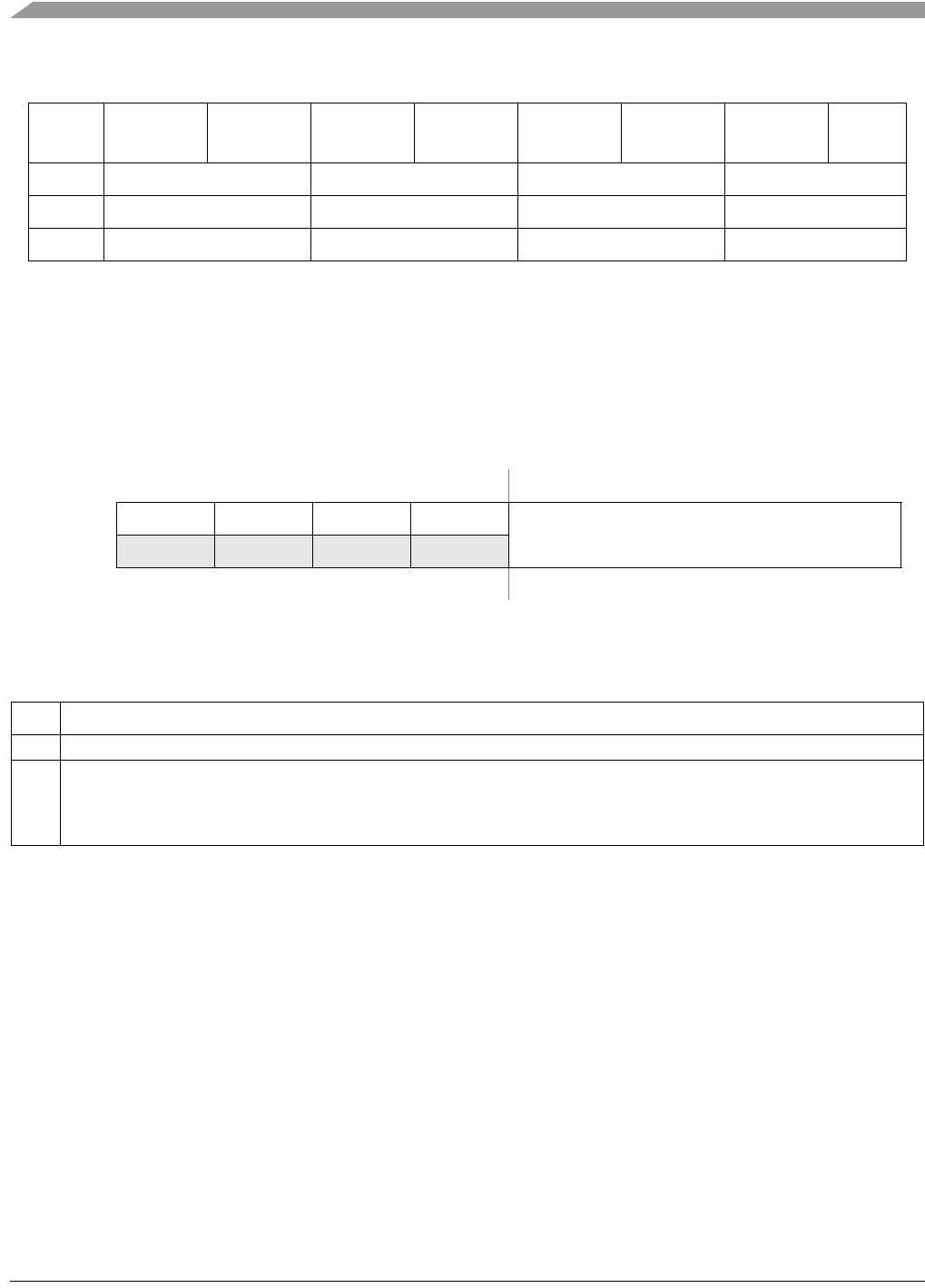

0x034 — — — —

0x038 — — — —

0x03C — — — —

IPSBAR

Offset: 0x0020 (MPR)

Access: read/write

76543210

R 0 0 0 0

MPR[3:0]

W

Reset:00000001

Figure 12-8. Master Privilege Register (MPR)

Table 12-9. MPR[n] Field Descriptions

Field Description

7–4 Reserved. Should be cleared.

3–0

MPR

Each 1-bit field defines the access privilege level of the given bus master n.

0 All bus master accesses are in user mode.

1 All bus master accesses use the sourced user/supervisor attribute.

Note: Bit 3 is reserved and should be cleared.

Table 12-8. SACU Register Memory Map (continued)

IPSBAR

Offset

[31:28] [27:24] [23:20] [19:16] [15:12] [11:8] [7:4] [3:0]