General Purpose Timer Module (GPT)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

21-4 Freescale Semiconductor

21.5.3 SYNCn

The SYNCn pin is for synchronization of the timer counter. It can be used to synchronize the counter with

externally-timed or clocked events. A high signal on this pin clears the counter.

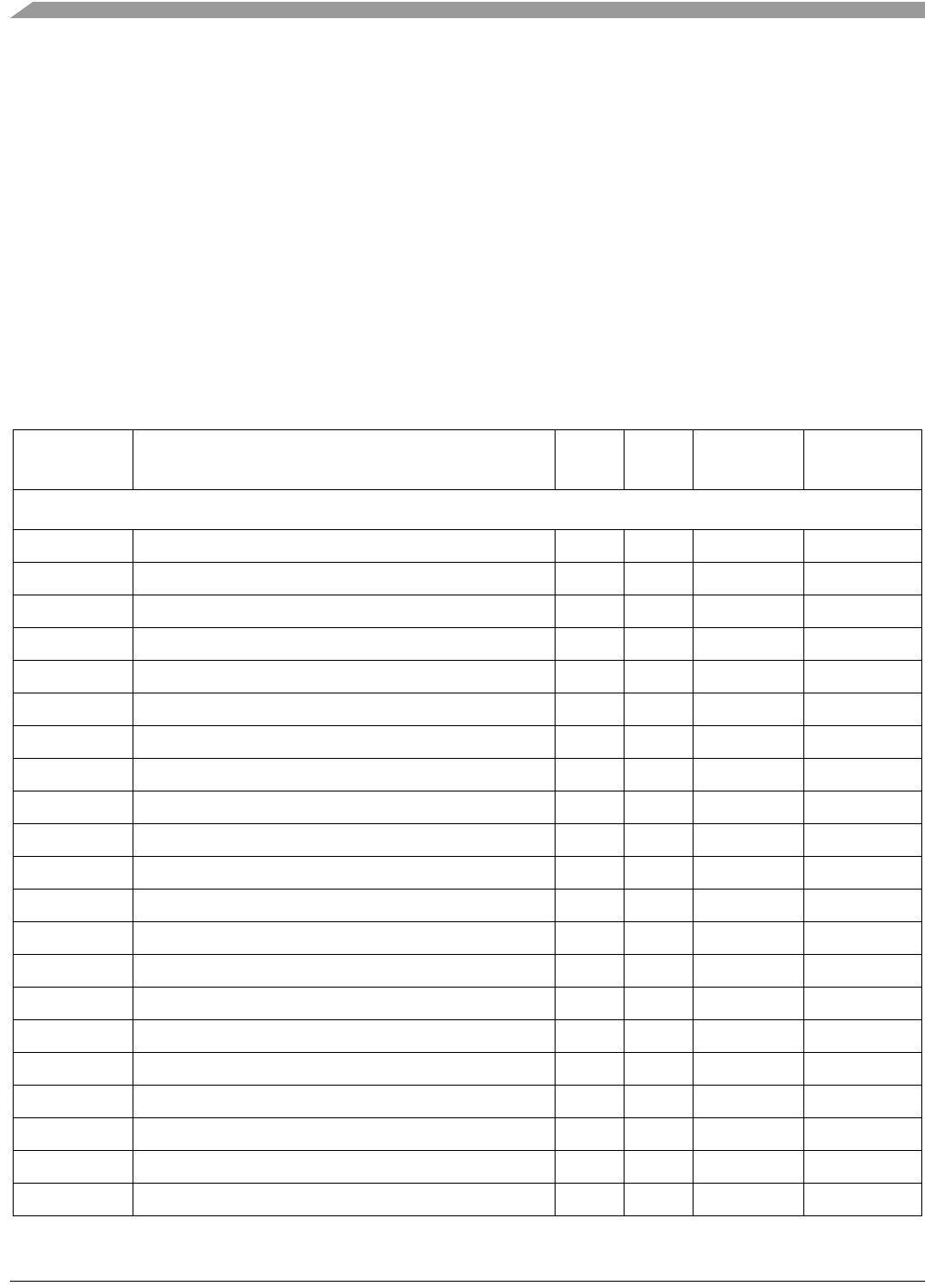

21.6 Memory Map and Registers

Table 21-3 shows the memory map of the GPT module. The base address for GPT is IPSBAR +

0x1A_0000.

NOTE

Reading reserved or unimplemented locations returns zeros. Writing to

reserved or unimplemented locations has no effect.

Table 21-3. GPT Memory Map

IPSBAR

Offset

1

Register

Width

(bits)

Access Reset Value Section/Page

Supervisor Mode Access Only

0x1A_0000 GPT IC/OC Select Register (GPTIOS) 8 R/W 0x00 21.6.1/21-5

0x1A_0001 GPT Compare Force Register (GPTCFORC) 8 R/W 0x00 21.6.2/21-6

0x1A_0002 GPT Output Compare 3 Mask Register (GPTOC3M) 8 R/W 0x00 21.6.3/21-6

0x1A_0003 GPT Output Compare 3 Data Register (GPTOC3D) 8 R/W 0x00 21.6.4/21-7

0x1A_0004 GPT Counter Register High (GPTCNTH)

2

8 R 0x00 21.6.5/21-7

0x1A_0005 GPT Counter Register Low (GPTCNTL)

2

8 R 0x00 21.6.5/21-7

0x1A_0006 GPT System Control Register 1 (GPTSCR1) 8 R/W 0x00 21.6.6/21-8

0x1A_0008 GPT Toggle-on-Overflow Register (GPTTOV) 8 R/W 0x00 21.6.7/21-9

0x1A_0009 GPT Control Register 1 (GPTCTL1) 8 R/W 0x00 21.6.8/21-9

0x1A_000B GPT Control Register 2 (GPTCTL2) 8 R/W 0x00 21.6.9/21-10

0x1A_000C GPT Interrupt Enable Register (GPTIE) 8 R/W 0x00 21.6.10/21-10

0x1A_000D GPT System Control Register 2 (GPTSCR2) 8 R/W 0x00 21.6.11/21-11

0x1A_000E GPT Flag Register 1 (GPTFLG1) 8 R/W 0x00 21.6.12/21-12

0x1A_000F GPT Flag Register 2 (GPTFLG2) 8 R/W 0x00 21.6.13/21-12

0x1A_0010 GPT Channel 0 Register High (GPTC0H)

2

8 21.6.14/21-13

0x1A_0011 GPT Channel 0 Register Low (GPTC0L)

2

8 21.6.14/21-13

0x1A_0012 GPT Channel 1 Register High (GPTC1H)

2

8 21.6.14/21-13

0x1A_0013 GPT Channel 1 Register Low (GPTC1L)

2

8 21.6.14/21-13

0x1A_0014 GPT Channel 2 Register High (GPTC2H)

2

8 21.6.14/21-13

0x1A_0015 GPT Channel 2 Register Low (GPTC2L)

2

8 21.6.14/21-13

0x1A_0016 GPT Channel 3 Register High (GPTC3H)

2

8 21.6.14/21-13