DMA Controller Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

17-4 Freescale Semiconductor

17.3.1 DMA Request Control (DMAREQC)

The DMAREQC register provides a software-controlled connection matrix for DMA requests. It logically

routes DMA requests from the DMA timers and UARTs to the four channels of the DMA controller.

Writing to this register determines the exact routing of the DMA request to the four channels of the DMA

modules.

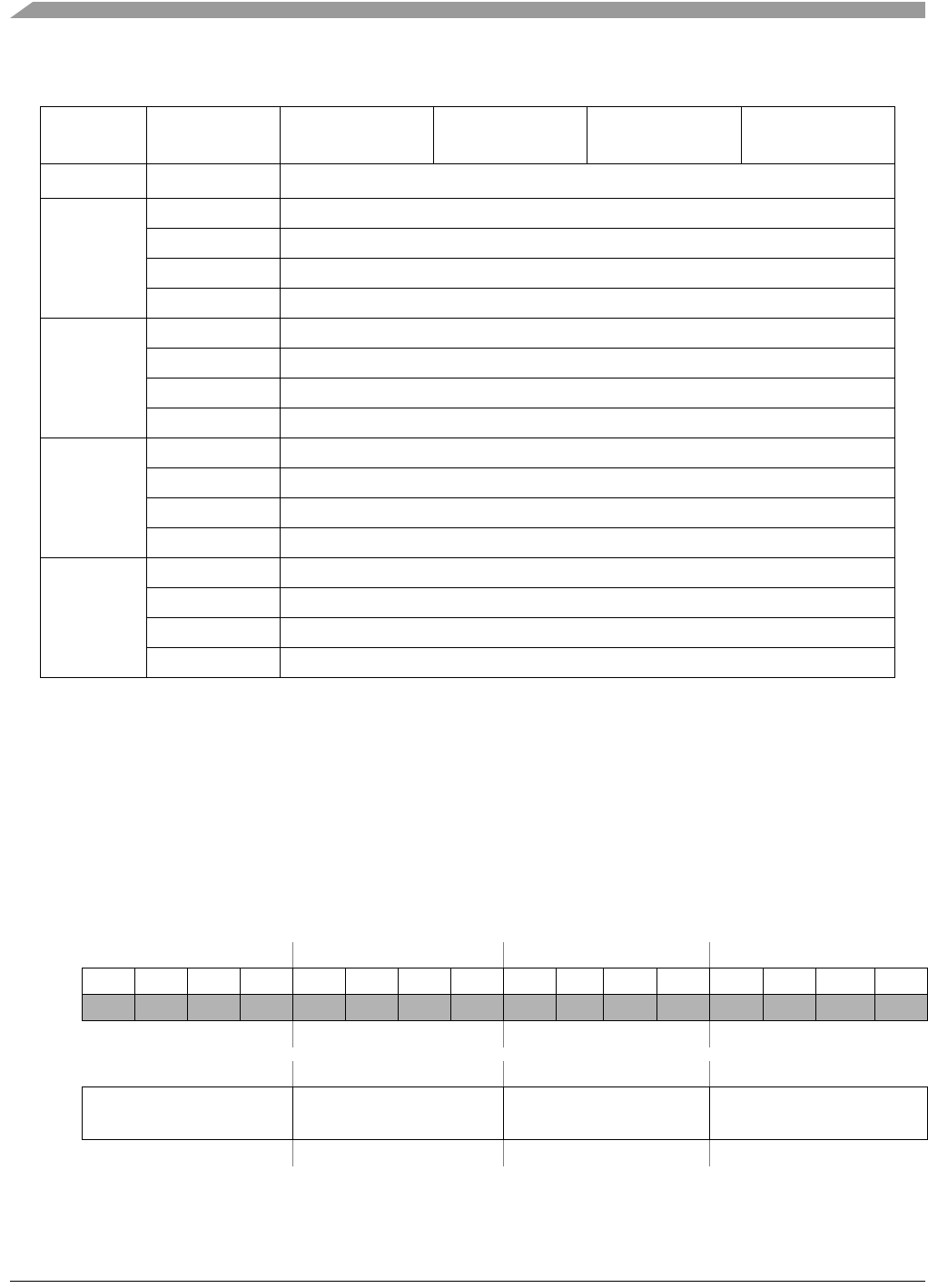

Table 17-1. Memory Map for DMA Controller Module Registers

DMA

Channel

IPSBAR Offset [31:24] [23:16] [15:8] [7:0]

— 0x00_0014

DMA Request Control Register (DMAREQC)

1

1

Located within the SCM, but listed here for clarity.

0 0x00_0100 Source Address Register 0 (SAR0)

0x00_0104 Destination Address Register 0 (DAR0)

0x00_0108 Byte Count Register 0 (BCR0) and DMA Status Register 0 (DSR0)

0x00_010C DMA Control Register 0 (DCR0)

1 0x00_0110 Source Address Register 1 (SAR1)

0x00_0114 Destination Address Register 1 (DAR1)

0x00_0118 Byte Count Register 1 (BCR1) and DMA Status Register 1 (DSR1)

0x00_011C DMA Control Register 1 (DCR1)

2 0x00_0120 Source Address Register 2 (SAR2)

0x00_0124 Destination Address Register 2 (DAR2)

0x00_0128 Byte Count Register 2 (BCR2) and DMA Status Register 2 (DSR2)

0x00_012C DMA Control Register 2 (DCR2)

3 0x00_0130 Source Address Register 3 (SAR3)

0x00_0134 Destination Address Register 3 (DAR3)

0x00_0138 Byte Count Register 3 (BCR3) and DMA Status Register 3 (DSR3)

0x00_013C DMA Control Register 3 (DCR3)

IPSBAR

Offset: 0x00_0014 (DMAREQC)

Access: read/write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R00000000000000 0 0

W

Reset00000000000000 0 0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

DMAC3 DMAC2 DMAC1 DMAC0

W

Reset00000000000000 0 0

Figure 17-3. DMA Request Control Register (DMAREQC)