ColdFire Flash Module (CFM)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 18-7

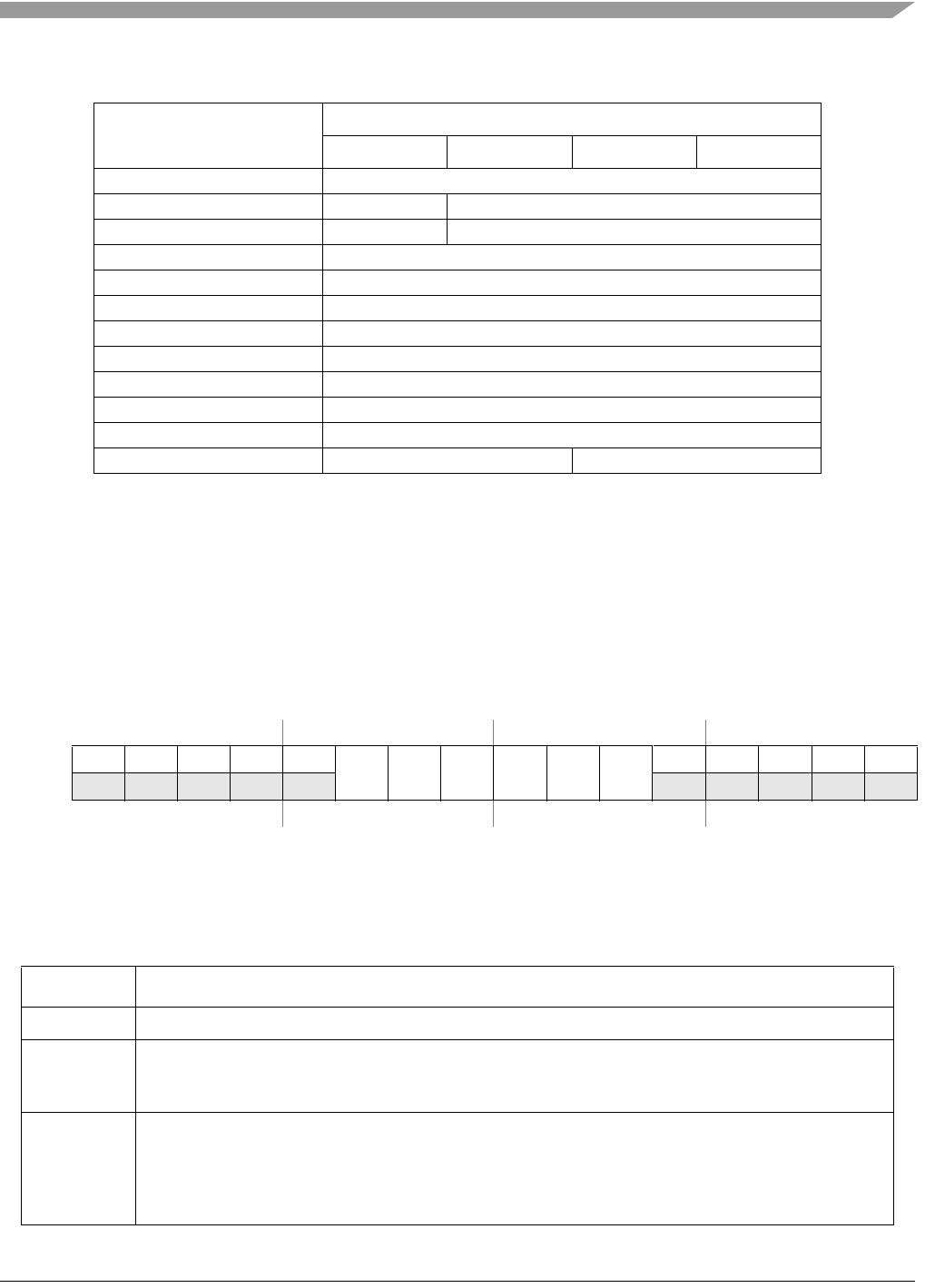

18.3.3 Register Descriptions

18.3.3.1 CFMMCR — CFM Module Configuration Register

The CFMMCR register is used to configure and control the operation of the internal bus interface.

CFMMCR register bits [10:5] are readable and writable with restrictions, while the remaining bits read 0

and are not writable.

0x1D_001C RESERVED

1

0x1D_0020 CFMUSTAT RESERVED

1

0x1D_0024 CFMCMD RESERVED

1

0x1D_0028 RESERVED

1

0x1D_002C RESERVED

1

0x1D_0030 RESERVED

1

0x1D_0034 RESERVED

1

0x1D_0038 RESERVED

1

0x1D_003C RESERVED

1

0x1D_0040 RESERVED

1

0x1D_0044 RESERVED

1

0x1D_0048 RESERVED

1

CFMCLKSEL

1

Access to reserved address locations generate a cycle termination transfer error.

IPSBAR

Offset: 0x1D_0000 (CFMMCR)

Access: User read/write

1514131211109876543210

R 00000LOCK PVIE AEIE CBEI

E

CCIE KEYA

CC

00000

W

Reset0000000000000000

Figure 18-4. CFM Module Configuration Register (CFMMCR)

Table 18-4. CFMMCR Field Descriptions

Field Description

15-11 Reserved, read as 0

10

LOCK

Write Lock Control. The LOCK bit is always readable and is set once.

1 = CFMPROT, CMFSACC, and CFMDACC registers are write-locked.

0 = CFMPROT, CMFSACC, and CFMDACC registers are writable.

9

PVIE

Protection Violation Interrupt Enable

The PVIE bit is always readable and writable. The PVIE bit enables an interrupt in case the protection

violation flag, PVIOL in the CFMUSTAT register, is set.

1 = An interrupt is requested when the PVIOL flag is set.

0 = PVIOL interrupt disabled.

Table 18-3. CFM Register Address Map

IPSBAR Offset

Register Bits

31 - 24 23 - 16 15 - 8 7 - 0