General Purpose I/O Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 13-5

13.6.2 Port Data Direction Registers (DDRn)

The DDRn registers control the direction of the port n pin drivers when the pins are configured for digital

I/O.

The DDRn registers with a full 8-bit implementation are shown in Figure 13-7. The remaining DDRn

registers use fewer than eight bits. Their bit definitions are shown in Figure 13-8, Figure 13-9,

Figure 13-10, and Figure 13-11. The fields are described in Table 13-3, which applies to all DDRn

registers.

The DDRn registers are read/write. At reset, all bits in the DDRn registers are cleared.

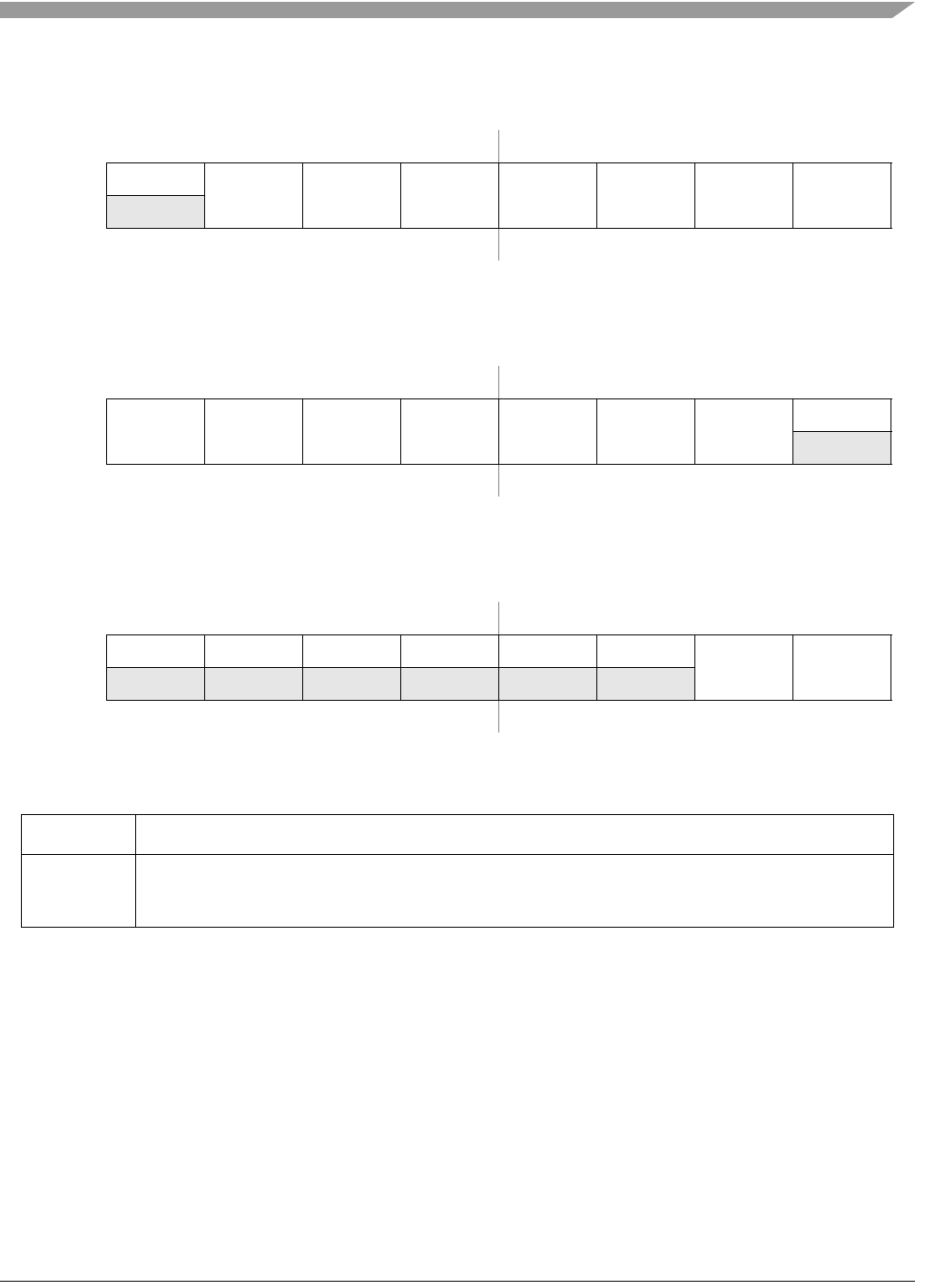

IPSBAR

Offset: 0x10_000C (PORTQS)

Access: User read/write

76543210

R 0

PORTn6 PORTn5 PORTn4PORTn3PORTn2PORTn1PORTn0

W

Reset:01111111

Figure 13-4. Port QS Output Data Register (PORTQS)

IPSBAR

Offset: 0x10_0008 (PORTNQ)

Access: User read/write

76543210

R

PORTn7 PORTn6 PORTn5 PORTn4PORTn3PORTn2PORTn1

0

W

Reset:11111110

Figure 13-5. Port NQ Output Data Register (PORTNQ)

IPSBAR

Offset: 0x10_000B (PORTAS)

Access: User read/write

76543210

R 0 0 0 000

PORTn1PORTn0

W

Reset:00000011

Figure 13-6. Port AS Output Data Register (PORTAS)

Table 13-2. PORTn Field Descriptions

Field Description

Portnx Data to be driven when the port pin is configured as a digital output.

1 Output is a logic 1

0 Output is a logic 0