Interrupt Controller Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 14-9

request, 0 = negate request) in the appropriate INTFRCn register. The assertion of an interrupt request via

the INTFRCn register is not affected by the interrupt mask register. The INTFRCn register is cleared by

reset.

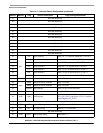

IPSBAR

Offset: 0x0C10 (INTFRCHn)

Access: Read/write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

INTFRCH[63:48]

W

Reset0000000000000000

1514131211109876543210

R

INTFRCH[47:32]

W

Reset0000000000000000

Figure 14-5. Interrupt Force Register High (INTFRCHn)

Table 14-7. INTFRCHn Field Descriptions

Field Description

31–0

INTFRCH

Interrupt force. Allows software generation of interrupts for each possible source for functional or debug purposes.

0 No interrupt forced on corresponding interrupt source

1 Force an interrupt on the corresponding source

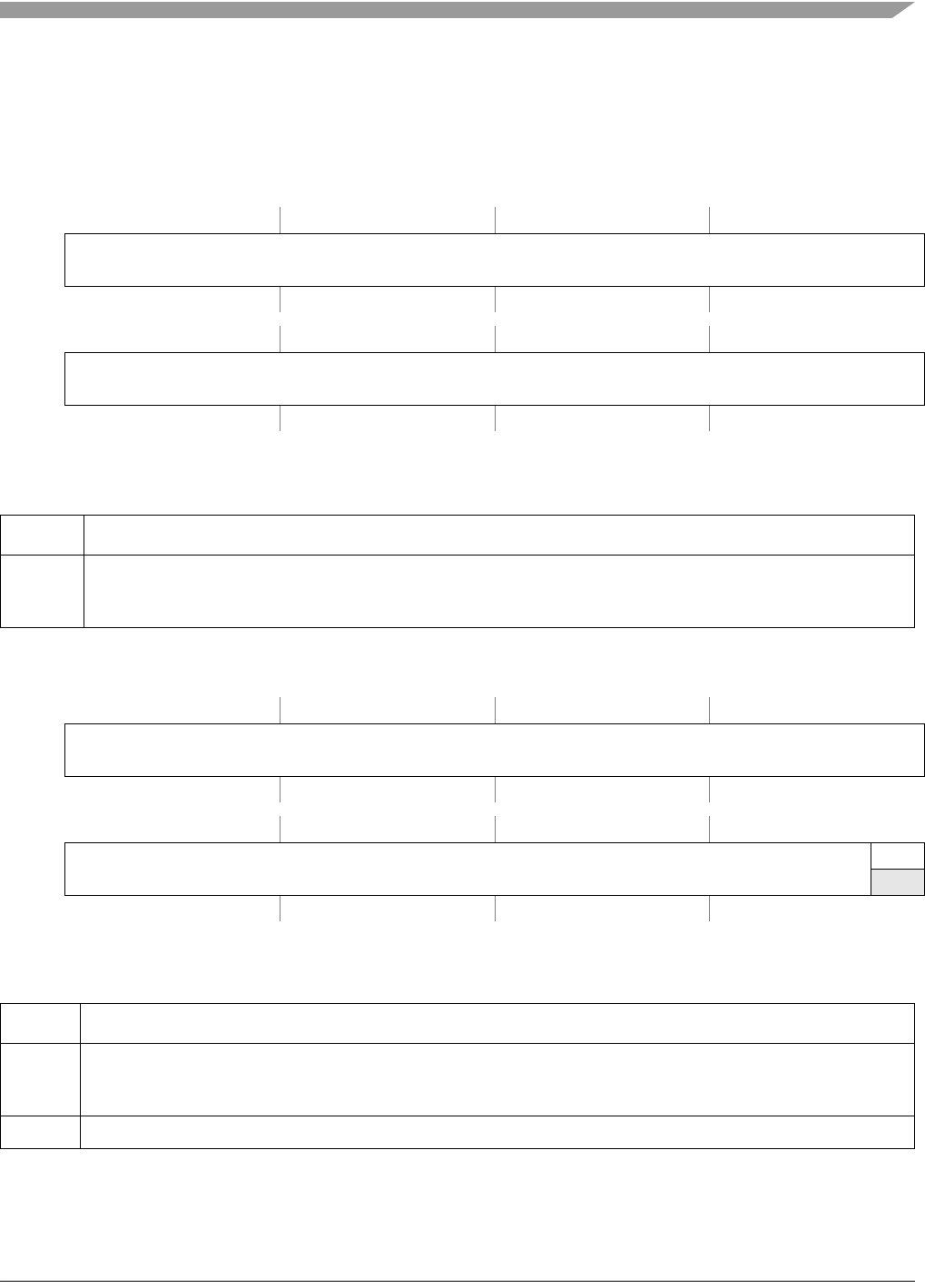

IPSBAR

Offset: 0x0C14 (INTFRCLn)

Access: Read/write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

INTFRCL[31:16]

W

Reset0000000000000000

1514131211109876543210

R

INTFRCL[15:1]

0

W

Reset0000000000000000

Figure 14-6. Interrupt Force Register Low (INTFRCLn)

Table 14-8. INTFRCLn Field Descriptions

Field Description

31–1

INTFRCL

Interrupt force. Allows software generation of interrupts for each possible source for functional or debug purposes.

0 No interrupt forced on corresponding interrupt source

1 Force an interrupt on the corresponding source

0 Reserved, should be cleared.