System Control Module (SCM)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 12-3

12.5 Register Descriptions

12.5.1 Internal Peripheral System Base Address Register (IPSBAR)

The IPSBAR specifies the base address for the 1-Gbyte memory space associated with the on-chip

peripherals. At reset, the base address is loaded with a default location of 0x4000_0000 and marked as

valid (IPSBAR[V]=1). If desired, the address space associated with the internal modules can be moved by

loading a different value into the IPSBAR at a later time.

0x002C Peripheral Access Control Register (PACR8) 8 R/W 0x00 12.7.3.2/12-14

0x0030 GPACR0 Register 8 R/W 0x00 12.7.3.3/12-16

0x0031 GPACR1 Register 8 R/W 0x00 12.7.3.3/12-16

1

Addresses not assigned to a register and undefined register bits are reserved for expansion.

2

The PPMRH, LPICR, PMRL, PPMRS, PPMRC, and IPSBMT are described in Chapter 8, “Power Management.”

3

Register must be addressed as a byte.

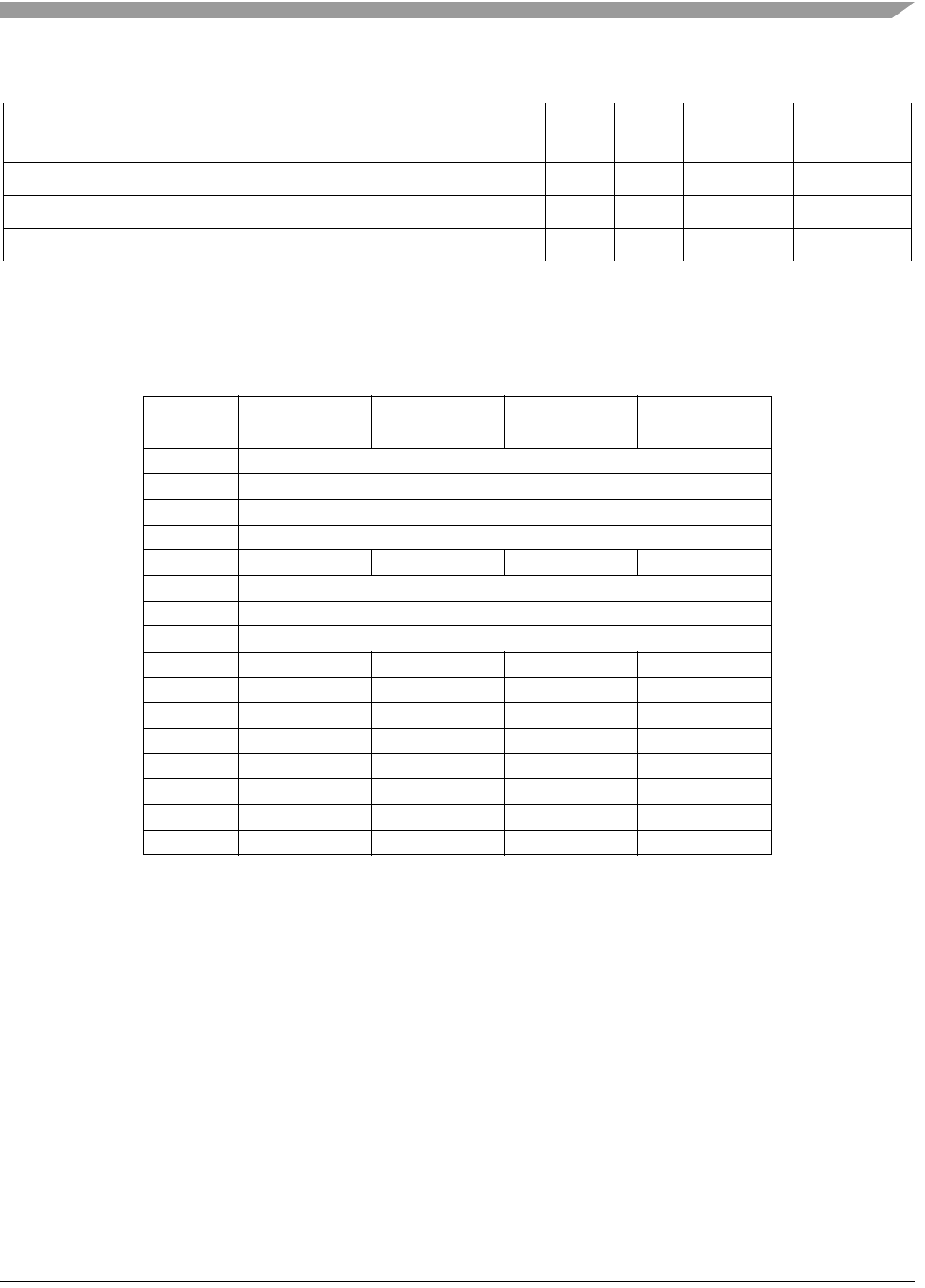

Table 12-2. Accessing as 32-Bit Registers

IPSBAR

Offset

[31:24] [23:16] [15:8] [7:0]

0x0000 IPSBAR

0x0004 —

0x0008 RAMBAR

0x000C PPMRH

1

1

The LPICR is described in Chapter 8, “Power Management.”

0x0010 CRSR CWCR LPICR

1

CWSR

0x0014 DMAREQC

2

2

The DMAREQC register is described in Chapter 17, “DMA Controller Module.”

0x0018 PPMRL

1

0x001C MPARK

0x0020 MPR PPMRS

1

PPMRC

1

IPSBMT

1,3

3

Register must be addressed as a byte.

0x0024 PACR0 PACR1 PACR2 PACR3

0x0028 PACR4 PACR5 PACR6 PACR7

0x002C PACR8 — — —

0x0030 GPACR0 GPACR1 — —

0x0034 — — — —

0x0038 — — — —

0x003C — — — —

Table 12-1. SCM Register Map (continued)

IPSBAR

Offset

1

Register

Width

(bits)

Access Reset Value Section/Page