8

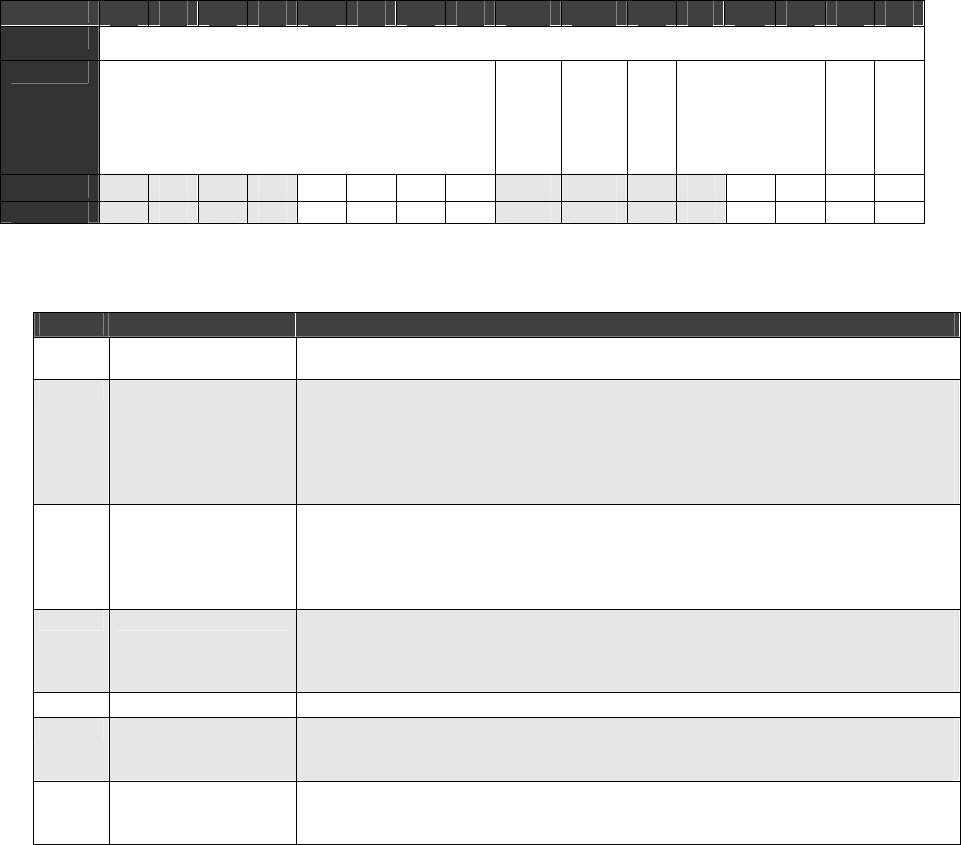

SPI_STAT Register

To clear a bit in the SPI_STAT register, write a 1 to that bit.

Table 2-6. SPI_STAT Register

BIT

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET

B804

FIELD

///

IRQ

OVERRUN

COL

///

TXRUN

SLVSEL

RESET

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW R R

Table 2-7. SPI_STAT Register Definitions

Bits Field Name Description

15:8 ///

Reserved

Always returns zero.

7 IRQ

Interrupt Request

1 = indicates the end of a master mode transfer, or that SLVSEL_N input has

gone HIGH on a slave transfer.

0 = indicates no end of a master mode transfer, or that SLVSEL_N input has not

gone HIGH on a slave transfer (default).

It takes two CPU clocks after SLVSEL_n changes to see the interrupt.

6 OVERRUN

Overrun

1 = SPIDAT register is written to while an SPI transfer is in progress or

SLVSEL_N goes active in master mode.

0 = SPIDAT register has not been written to or SLVSEL_N has not gone active in

master mode (default).

5 COL

Collision

1 = a master mode collision has occurred between multiple SPI masters (SLVSEL

is active while MSTEN=1).

0 = a master mode collision has not occurred (default).

4:2 ///

Reserved

1 TXRUN

Transmitter Running

1 = master mode operation underway.

0 = idle (default).

0 SLVSEL

SLVSEL Pin

Corresponds to the SLVSEL (MSCS*) pin on SPI core (pin is normally inverted at

the I/O pin).