19

Receiving Each Data Byte

After receiving each data byte, the IFLG is set and one of three status codes in Table 3-6 is in

the Status register.

When all bytes are received, set the STP bit by writing a 1 to it in the Control register. The I

2

C

controller:

Transmits a STOP condition

Clears the STP bit

Returns to the idle state

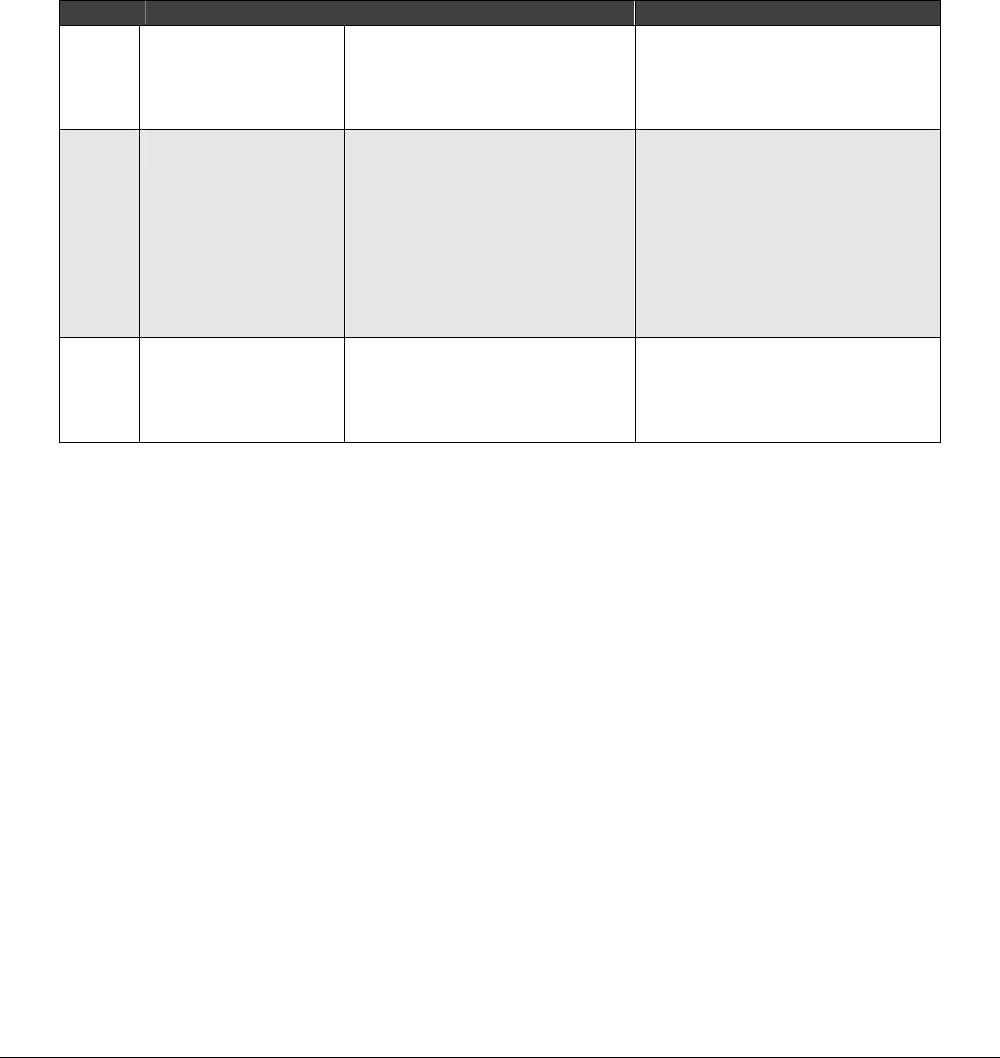

Table 3-6. Codes After Receiving Each Data Byte

Code I

2

C State Microprocessor Response Next I

2

C Action

50h Data byte received,

ACK transmitted

Read DATA, clear IFLG, AAK=0

OR

Read DATA, clear IFLG, AAK=1

Receive data byte, transmit not ACK

Receive data byte, transmit ACK

58h Data byte received, Not

ACK transmitted

Read DATA, set STA, clear IFLG

OR

Read DATA, set STP, clear IFLG

OR

Read DATA, set STA & STP, clear

IFLG

Transmit repeated START

Transmit STOP

Transmit STOP then START

38h Arbitration lost in not

ACK bit

Clear IFLG

OR

Set STA, clear IFLG

Return to idle

Transmit START when bus free

Slave Transmit Mode

In the slave transmit mode, a number of bytes are transmitted to a master receiver.

The I

2

C controller enters slave transmit mode when it receives its own slave address and a read

bit after a START condition. The I

2

C controller then transmits an acknowledge bit and sets the

IFLG bit in the Control register. The Status register contains the status code A8h.

Note: If the I

2

C controller has an extended slave address (signified by F0h - F7h in the Slave

Address register), it transmits an acknowledge after receiving the first address byte, but does

not generate an interrupt; the IFLG is not set and the status does not change. Only after

receiving the second address byte does The I

2

C controller generate an interrupt and set the

IFLG bit and status code as described above.

The I

2

C controller can also enter slave transmit mode directly from a master mode if arbitration

is lost in master mode during address transmission, and both the slave address and read bit are

received. The status code in the Status register is B0h.

After the I

2

C controller enters slave transmit mode:

1. The Data register loads the data byte to be transmitted, then IFLG clears.

2. The I

2

C controller transmits the byte.

3. The I

2

C controller receives or does not receive an acknowledge.

If the I

2

C controller receives an acknowledge: