64

Tx Message Registers

Table 5-5 shows TxMessage_0 registers. The registers for TxMessage_1 and TxMessage_2

are identical except for the offsets.

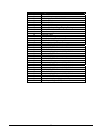

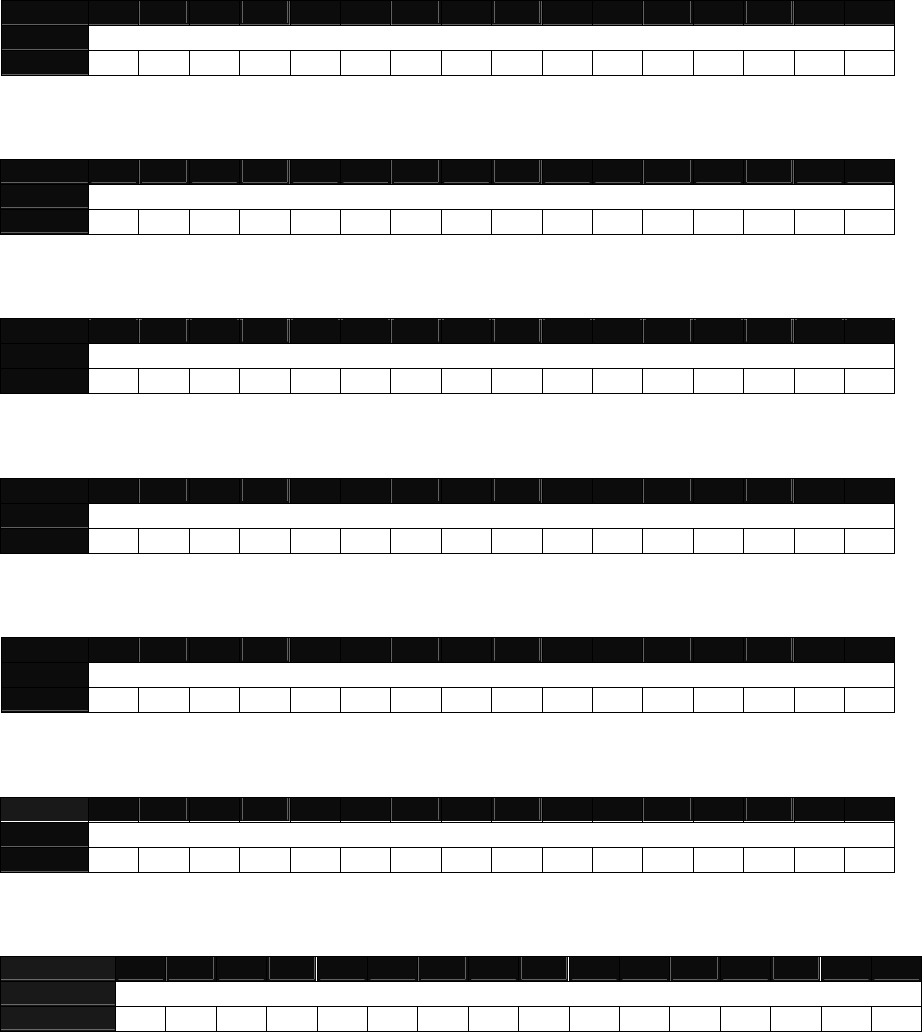

Table 5-5. TxMessage_0:ID28

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET 00h

FIELD ID28 ID27 ID26 ID25 ID24 ID23 ID22 ID21 ID20 ID19 ID18 ID17 ID16 ID15 ID14 ID13

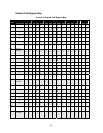

Table 5-6. TxMessage_0:ID12

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET 02h

FIELD ID12 ID11 ID10 ID09 ID08 ID07 ID06 ID05 ID04 ID03 ID02 ID01 ID00 /// /// ///

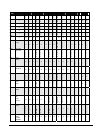

Table 5-7. TxMessage_0:Data 55

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET 04h

FIELD D55 D54 D53 D52 D51 D50 D49 D48 D63 D62 D61 D60 D59 D58 D57 D56

Table 5-8. TxMessage_0:Data 39

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET 06h

FIELD D39 D38 D37 D36 D35 D34 D33 D32 D47 D46 D45 D44 D43 D42 D41 D40

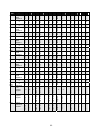

Table 5-9. TxMessage_0:Data 23

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET 08

FIELD D23 D22 D21 D20 D19 D18 D17 D16 D31 D30 D29 D28 D27 D26 D25 D24

Table 5-10. TxMessage_0:Data 7

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET 0A

FIELD D07 D06 D05 D04 D03 D02 D01 D00 D15 D14 D13 D12 D11 D10 D09 D08

Table 5-11. TxMessage_0:RTR

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET 0C

FIELD /// /// /// /// /// /// /// /// /// /// RTR IDE DLC3 DLC2 DLC1 DLC0