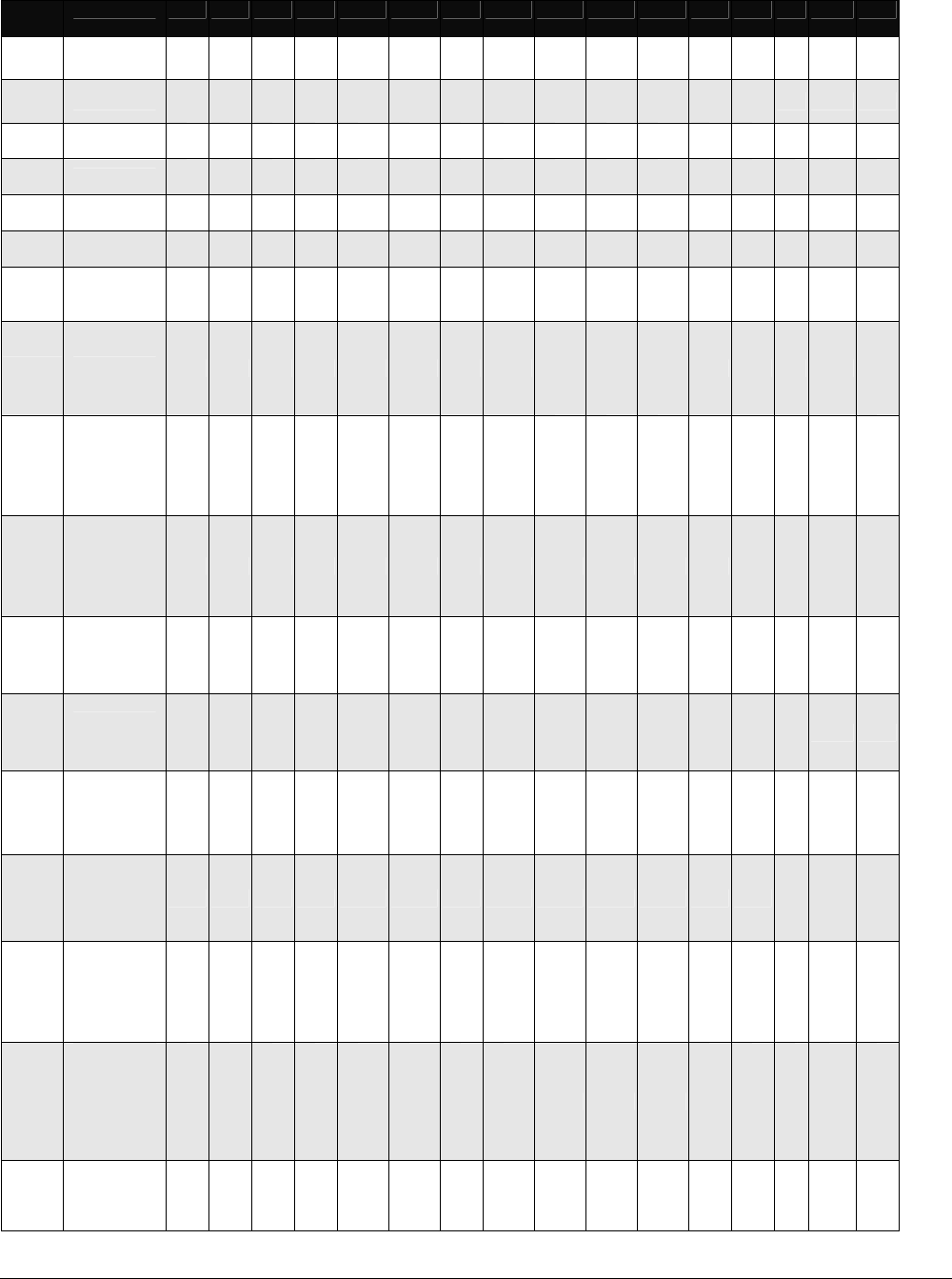

61

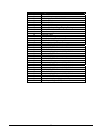

Hex

Offset

Register 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0x30

RX Msg

ID28

ID27

ID26

ID25

ID24

ID23

ID22

ID21

ID20

ID19

ID18

ID17

ID16

ID15

ID14

ID13

0x32

///

ID12

ID11

ID10

ID09

ID08

ID07

ID06

ID05

ID04

ID03

ID02

ID01

ID00

/// /// ///

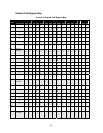

0x34

///

D55

D54

D53

D52

D51

D50

D49

D48

D63

D62

D61

D60

D59

D58

D57

D56

0x36

///

D39

D38

D37

D36

D35

D34

D33

D32

D47

D46

D45

D44

D43

D42

D41

D40

0x38

///

D23

D22

D21

D20

D19

D18

D17

D16

D31

D30

D29

D28

D27

D26

D25

D24

0x3a

///

D07

D06

D05

D04

D03

D02

D01

D00

D15

D14

D13

D12

D11

D10

D09

D08

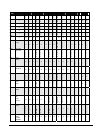

0x3c

/// /// /// /// /// ///

AFI_2

AFI_1

AFI_0

/// ///

RTR

IDE

DLC_3

DLC_2

DLC_1

DLC_0

0x3e

RX Msg

Flags

/// /// /// /// /// /// /// ///

Fifo_Lvl_2

Fifo_Lvl_1

Fifo_Lvl_0

/// /// /// ///

MsgAval

0x40

TX & RX

Error Cnt

rx_er_cnt_7

rx_er_cnt_6

rx_er_cnt_5

rx_er_cnt_4

rx_er_cnt_3

rx_er_cnt_2

rx_er_cnt_1

rx_er_cnt_0

tx_er_cnt_7

tx_er_cnt_6

tx_er_cnt_5

tx_er_cnt_4

tx_er_cnt_3

tx_er_cnt_2

tx_er_cnt_1

tx_er_cnt_0

0x42

Error

Status

/// /// /// /// /// /// /// /// /// /// /// ///

Rxgte96

Txgte96

error_stat_1

error_stat_0

0x44

TX/ RX

Msglevel

/// /// /// /// /// /// /// /// /// /// /// ///

rx_level_1

rx_level_0

tx_level_1

tx_level_0

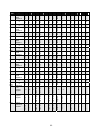

0x46

IRQ flags

rx_msg

tx_msg

tx_xmit2

tx_xmit1

tx_xmit0

bus_off

crc_error

form_error

ack_error

stuff_error

bit_error

rx_ovr

ovr_load

arb_loss

/// ///

0x48

IRQ

Enb.

Reg.

rx_msg

tx_msg

tx_xmit2

tx_xmit1

tx_xmit0

bus_off

crc_error

form_error

ack_error

stuff_error

bit_error

rx_ovr

ovr_load

arb_loss

///

int_enable

0x4a

CAN

Mode

/// /// /// /// /// /// /// /// /// /// /// /// ///

Loop_Back

Passive

Run

0x4c

CAN

Bit

Rate

Divisor

/// /// /// /// ///

cfg_bitrate_10

cfg_bitrate_9

cfg_bitrate_8

cfg_bitrate_7

cfg_bitrate_6

cfg_bitrate_5

cfg_bitrate_4

cfg_bitrate_3

cfg_bitrate_2

cfg_bitrate_1

cfg_bitrate_0

0x4e

CAN

tsegs

ovr_wrt_msg

cfg_tseg2_2

cfg_tseg2_1

cfg_tseg2_0

cfg_tseg1_3

cfg_tseg1_2

cfg_tseg1_1

cfg_tseg1_0

/// /// ///

auto-restart

cfg_sjw_1

cfg_sjw_1

sample_mode

edge_mode

0x50

Acceptance

Filter

Enable

Register

/// /// /// /// /// /// /// /// /// /// /// /// ///

AFE_2

AFE_1

AFE_0