82

Error Capture Register

The Error Capture register captures the most recent error event with the frame reference

pointer, rx- and tx-mode and the associated error code.

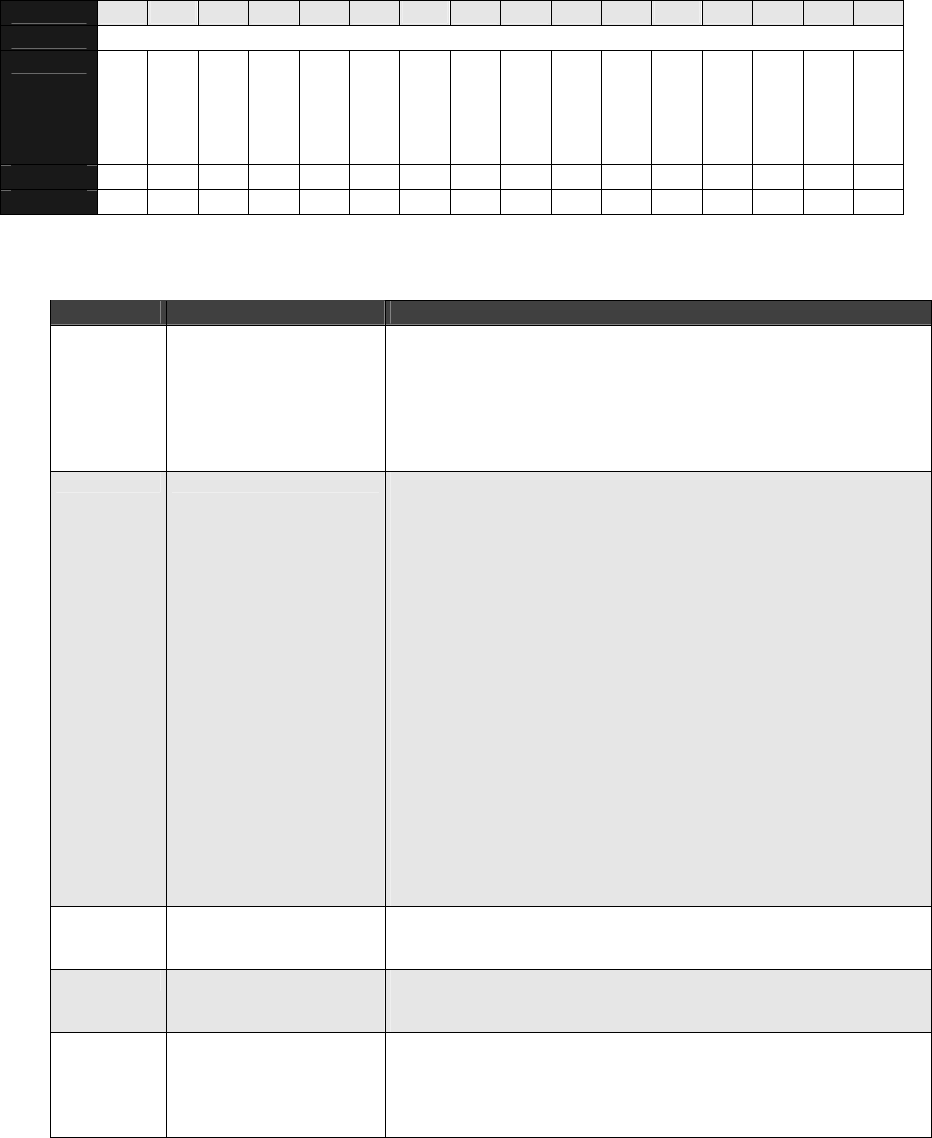

Table 5-62. Error Capture Register

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET 78h

FIELD

ERR2

ERR1

ERR0

FR4

FR3

FR2

FR1

FR0

TX_MOD

RX_MOD

FRB5

FRB4

FRB3

FRB2

FRB1

FRB0

RESET 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

Table 5-63. Error Capture Register Definitions

Bits Field Name Description

15:13 Err[2:0]

Error_code

000 = no error (default)

001 = crc_err

010 = form_err

011 = ack_err

100 = stuff_err

101 = bit_err

12:8 FR[4:0]

frame_ref_Field

This is the frame reference a incoming or outgoing CAN message.

Values are:

00000 = stopped

00001 = synchronize

00101 = interframe

00110 = bus_idle

00111 = start_of_frame

01000 = arbitration

01001 = control

01010= data

01011 = crc

01100 = ack

01101 = end_of_frame

10000 = error_flag

10001 = error_echo

10010 = error_del:

11000 = overload_flag

11001 = overload_echo

11010 = overload_del

Other codes are not used.

7 TX_MOD

TX Mode

1 = transmitting data.

0 = not in TX mode (receiving or idle).

6 RX_MOD

RX Mode

1 = receiving data.

0 = not in RX mode (transmitting or idle).

5:0 FRB[5:0]

frame_ref_bit_nr

A 6-bit vector that counts the bit numbers in one field.

Example: if field = “data” = “01010”, “bit_nr” = “000000”, and

“tx_mode” = ‘1’, it indicates that the first data bit is being

transmitted.