80

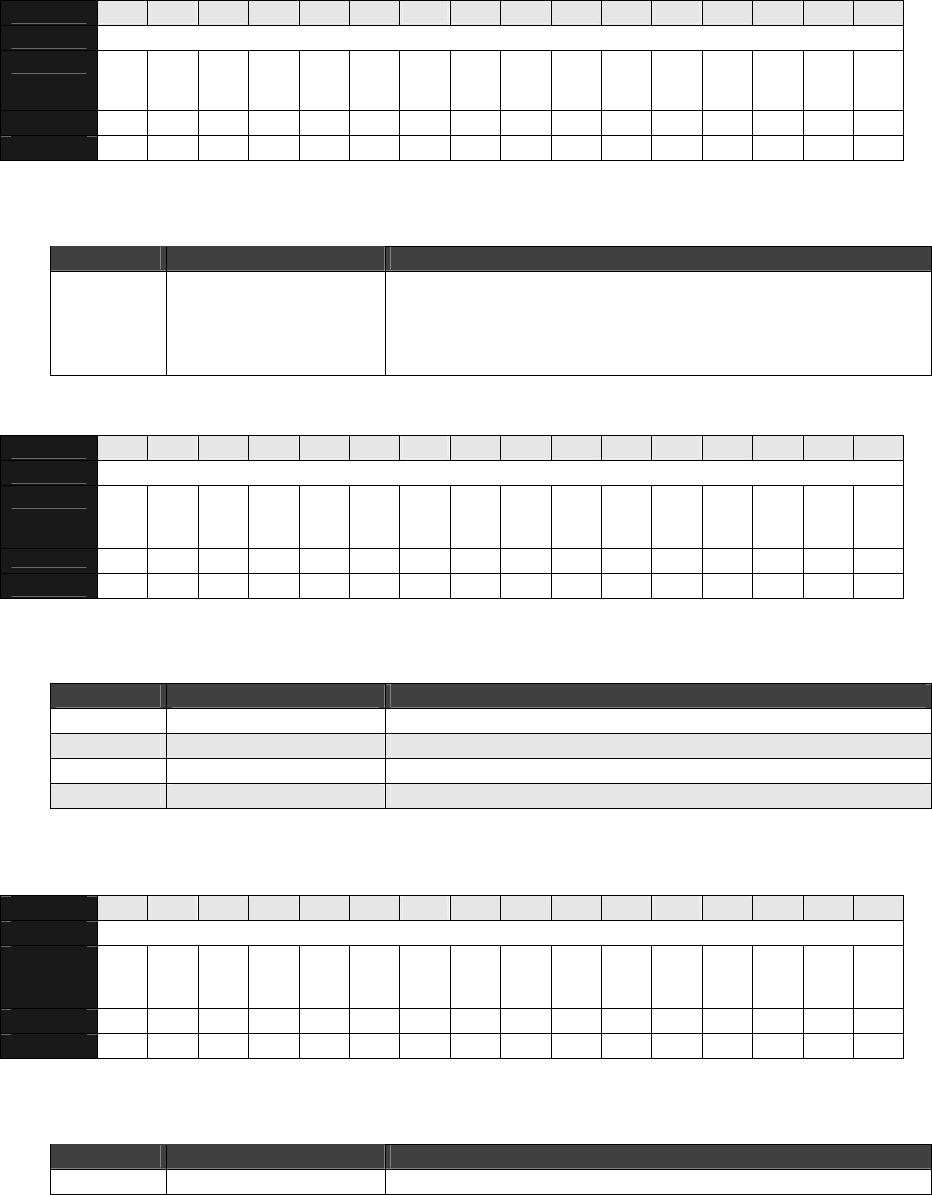

Table 5-54. Acceptance Code Register

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET 58h

FIELD

ID28

ID27

ID26

ID25

ID24

ID23

ID22

ID21

ID20

ID19

ID18

ID17

ID16

ID15

ID14

ID13

RESET 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

Table 5-55. Acceptance Code Register Definitions

Bits Field Name Description

15:0 ID[28:13]

Incoming Bit Check

1 = incoming bit is “don’ t care.”

0 = incoming bit is checked against the respective ACR. If the

incoming bit and the respective ACR are not the same, the

message is discarded.

Table 5-56. Acceptance Mask Register: ID12

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET 5Ah

FIELD

ID12

ID11

ID10

ID09

ID08

ID07

ID06

ID05

ID04

ID03

ID02

ID01

ID00

IDE

RTR

///

RESET 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

Table 5-57. Acceptance Mask Register: ID12 Definitions

Bits Field Name Description

15:3 ID[12:0]

Message Data

2 IDE

Extended Identifier Bit

1 RTR

Remote Bit

0 ///

Reserved

Table 5-58. Acceptance Mask Register: Data 55

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET 5Ch

FIELD

D55

D54

D53

D52

D51

D50

D49

D48

D63

D62

D61

D60

D59

D58

D57

D56

RESET 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

Table 5-59. Acceptance Mask Register: Data 55 Definitions

Bits Field Name Description

15:0 D[55:56]

Message Data