9

SPI_SSEL Register

SPI_SSEL is the Slave Select Bit Count register.

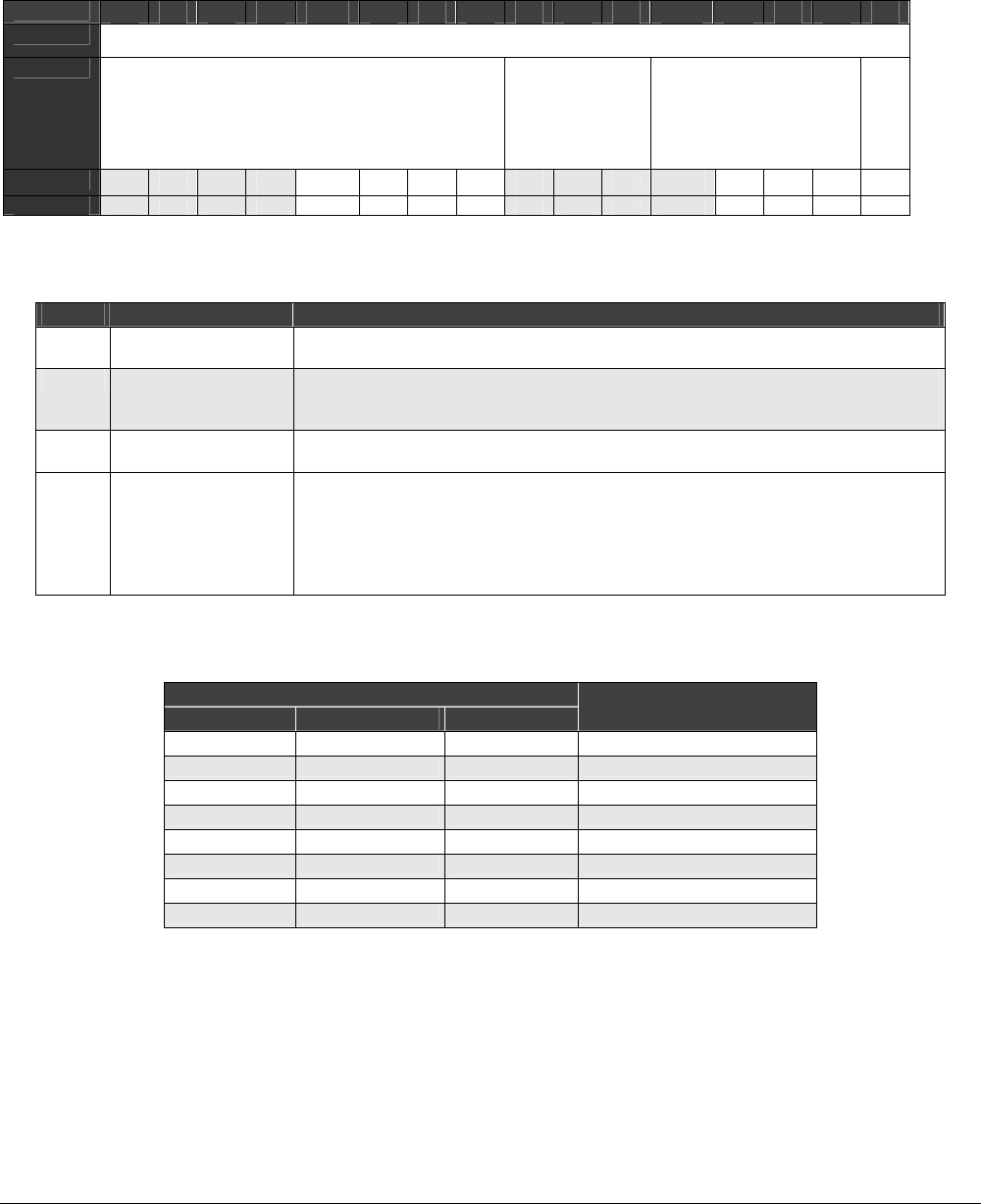

Table 2-8. SPI_SSEL Register

BIT

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET

B806

FIELD

/// BCNT[2:0] ///

SELECTO

RESET

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW RW

Table 2-9. SPI_SSEL Register Definitions

Bits Field Name Description

15:8 ///

Reserved

Always returns zero.

7:6 BCNT[2:0]

Bit Shift Count

Controls the number of bits shifted between the master and slave device during a

transfer, when this device is the master. See Table 2-10.

5:1 ///

Reserved

Always returns zero.

0 SELECTO

SelectO Signal

This bit is the select output for master mode.

1 = this bit drives the SLVSEL pin active.

0 = this bit inactivates SLVSEL (default).

This bit is not used with Autodrv. If using Autodrv, leave this bit set to 0. The

INVCS is used to invert the SLVSEL for active LOW devices.

Table 2-10. BCNT Bit Settings

BCNT[2:0]

Bit [2] Bit [1] Bit [0]

Number of Bits Shifted

0 0 0 8 (default)

0 0 1 1

0 1 0 2

0 1 1 3

1 0 0 4

1 0 1 5

1 1 0 6

1 1 1 7