78

Acceptance Filter and Acceptance Code Mask

Three programmable Acceptance Mask and Acceptance Code register (AMR/ACR) pairs filter

incoming messages. The acceptance mask register (AMR) defines whether the incoming bit is

checked against the acceptance code register (ACR).

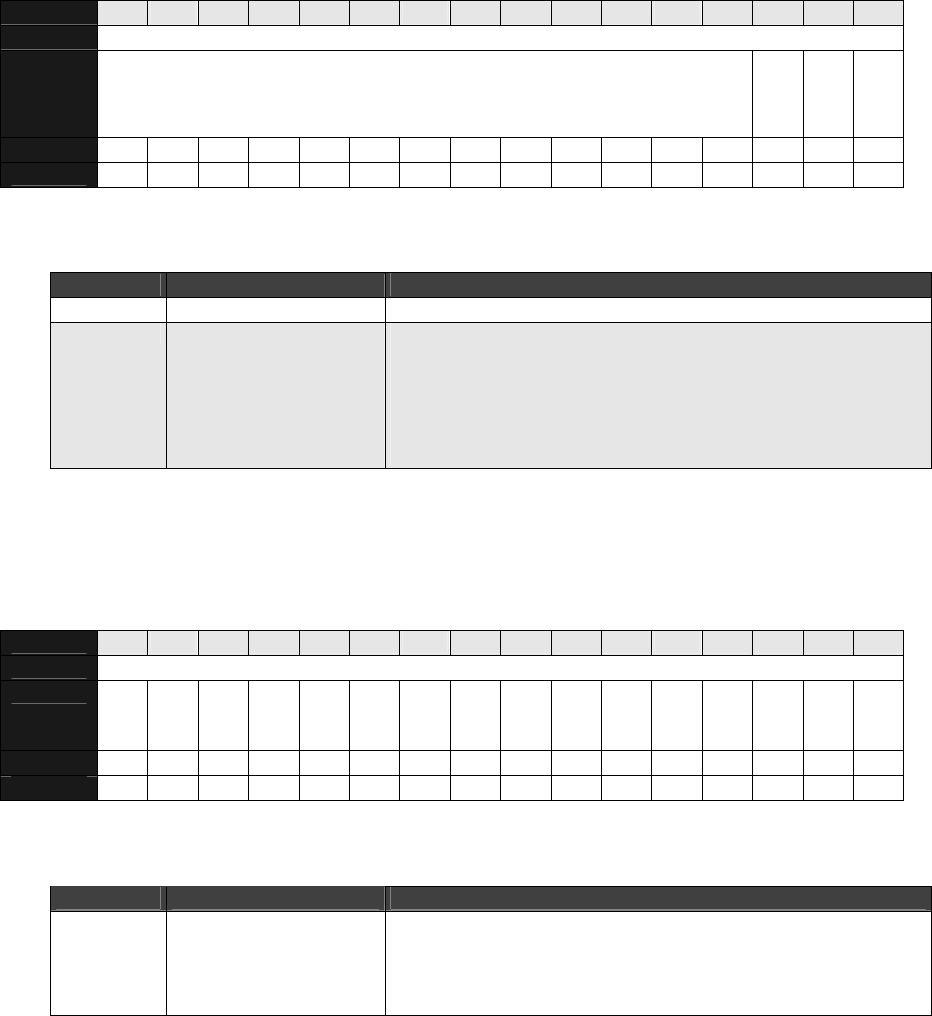

Table 5-46. Acceptance Filter Enable Register

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET 50h

FIELD

///

AFE2

AFE1

AFE0

RESET 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

Table 5-47. Acceptance Filter Enable Register Definitions

Bits Field Name Description

15:3 ///

Reserved

2:0 AFE[2:0]

Acceptance Filter Enable

Each Acceptance Mask register can be enabled with this flag.

1 = acceptance filter is enabled.

0 = acceptance filter is disabled.

If all three message filters are disabled, no messages are received.

To receive all messages, one message filter must be enabled and

programmed with all its fields as “don’ t care.”

The following tables show the Acceptance Mask Register for AMR0 and the Acceptance Code

Register ACR0. The registers for AMR1/ACR1 and AMR2/ACR2 are identical except for the

offsets. See the complete register table at the start of this section.

Table 5-48. Acceptance Mask 0 Register

BIT 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OFFSET 52h

FIELD

ID28

ID27

ID26

ID25

ID24

ID23

ID22

ID21

ID20

ID19

ID18

ID17

ID16

ID15

ID14

ID13

RESET 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

Table 5-49. Acceptance Mask 0 Register Definitions

Bits Field Name Description

15:0 ID[28:13]

Incoming Bit Check

1 = incoming bit is “don’ t care.”

0 = incoming bit is checked against the respective ACR. If the

incoming bit and the respective ACR are not the same, the

message is discarded.